前の10件 | -

beagleboard を触ろう - CPU キャッシュ [組み込みソフト]

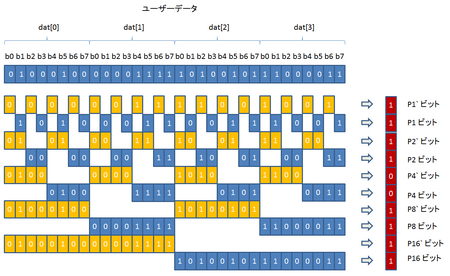

Cortex-A8 は、L1 命令キャッシュ、L1 データキャッシュ、命令/データ 共用 の L2 キャッシュを持っています。

それぞれのキャッシュサイズは、コプロセッサー cp15 の Cache Size Identification Register を読み出すことにより、知ることができます。

cp15 のレジスタには、mrc, mcr 命令でアクセスすることができます。

Cache Size Identification Register からは、キャッシュに関するサイズ以外の属性も読み出すことが出来ます。

beagleboard で実際に読み出してみると、以下のようになりました:

※

WT = Write Through サポート

WB = Write Back サポート

RA = Read Allocation サポート

WA = Write Allocation サポート

キャッシュサイズは、セット数 * ウェイ数 * ラインサイズ により算出されます。

例えば L1 命令キャッシュの場合、64 * 4 * 64 = 16384 バイトです。

キャッシュを有効にする方法は、命令キャッシュとデータキャッシュ・統一キャッシュで異なります。

基本的には、Control Register の I ビット、C ビット、Auxiliary Control Register の L2EN ビットが有効/無効を決定するのですが。

命令キャッシュは、I ビットを立てるだけで有効化することができます。

しかし、データキャッシュ・統一キャッシュは、C ビット/L2EN ビットを立てるだけでは有効化できません。

C ビット/L2EN ビットを立てるとともに、MMU も有効にしてやる必要があります。

キャッシュの有効・無効は、次のようなルールに従います:

MMU 稼働の場合

- L1 命令キャッシュは、SCTRL.I ビットの 1/0 によって有効/無効が決まる

- L1 データキャッシュは、SCTRL.C ビットの 1/0 によって有効/無効が決まる

- L2 統一キャッシュは、SCTRL.C ビットが 1 かつ Auxiliary SCTRL.L2EN ビットが 1 の場合は有効、それ以外の組み合わせの場合は無効

MMU 非稼働の場合

- L1 命令キャッシュは、SCTRL.I ビットの 1/0 によって有効/無効が決まる

- L1 データキャッシュは、SCTRL.C ビットの 1/0 によらず、無効になる

- L2 統一キャッシュは、SCTRL.C ビットおよび Auxiliary SCTRL.L2EN ビットの 1/0 によらず、無効になる

※SCTRL = Control Register, Auxiliary SCTRL = Auxiliary Control Register は、コプロセッサー cp15 のレジスタです。

L1 命令キャッシュは、簡単に有効にすることができますが、L1 データキャッシュ、L2 統一キャッシュは MMU を有効化しないと有効にできないので、多少面倒です。

なお、L2 を統一キャッシュと言っているのは、命令データとロード・ストアデータの両方を持つからです。

※

x-loader で、キャッシュはどうなっているかというと、、、

x-loader では、MMU を有効にしていませんので、L1 データキャッシュおよび L2 統一キャッシュは無効です。

L1 命令キャッシュは、有効にしています。

同時に、分岐予測も有効にしています。

MMU を有効にするには、ページテーブルが必要です。

一番簡単なページテーブルは、すべて 16MB のスーパーセクションで構成し、仮想アドレス=物理アドレスとなるようにする構成でしょう。

これだと、4GB のアドレス空間をカバーするのに必要なページテーブルのサイズは、1KB で済みます。

さて、それではこれから、キャッシュの有効化方法、無効化方法について、触れていきます。

きっちりやろうとすると、意外とめんどくさいです。

キャッシュ有効化方法

キャッシュを有効化するには、基本的にはキャッシュ有効化ビットを立てればいいのですが、その前にキャッシュを空にしておく必要があります。

さもないと、キャッシュ中のゴミが、キャッシュ有効後にメインメモリに排出されてしまいます。

キャッシュを空にする動作は invalidate と言いますが、invalidate をどのように行うかがキャッシュ有効化時の考慮点です。

そもそも、L1 キャッシュ、L2 キャッシュともに invalidate する必要があるのかどうか?という点から考えてみる必要があります。

そのために、まず、リセット時にキャッシュがどうなるか、知らなければなりません。

ARM ARM の「B2.2.2 キャッシュの動作 → リセット時のキャッシュの動作」を見てみると、

・すべてのキャッシュはリセット時に非稼働になります。

・実装では、特定のキャッシュ初期化ルーチンを使用して、キャッシュを稼働させる前にその記憶域アレイを無効にすることが必要な場合があります。必要な初期化ルーチンの詳細な形式は実装定義ですが、このルーチンはデバイスのドキュメントの一部として明示的に文書化する必要があります。

とあります。

「デバイスのドキュメント」に相当すると思われる Cortex-A8 TRM を見てみると、L1 キャッシュに関しては、特に初期化に関しての記述はありません。

また、L2 キャッシュに関しても、Auxiliary Control Register の L2EN ビットを立ててから、Control Register の C ビットを立てよ、との記述があるくらいです (8.3 Enabling and disabling the L2 cache controller)。

そこで、さらに OMAP35x TRM を見てみると、

・L2 キャッシュを使用するには、事前に L2 キャッシュのデータをすべて invalidate しなくてはならない

・BootROM コードに、L2 キャッシュを invalidate するサービスを用意しておくので、パワーオンリセット後、もしくはリセット後に呼びなさい

・そのサービスは、r12 レジスタに 1 をセットした状態で SMI 命令を発行すると呼び出すことができる

とあります (25.4.1 Booting Overview の Caution)。

SMI は、セキュアモニタ命令であり、BootROM コードで実装されている L2 キャッシュの invalidate サービスが、モニターモードで実装されているため、SMI 命令を実行する必要があります。

実際には、SMI 命令ではなく、SMC 命令を使用します。

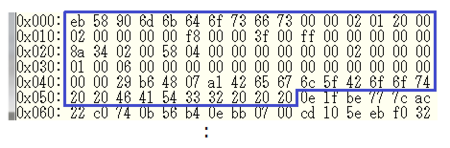

実装コードは、以下のようなアセンブリコードになります:

SMC 命令は、ARM ARM には、「SMC (以前の SMI)」 と記載されています。

SMC 命令は、即値引数を一つ取ります。

この即値引数に関しては、同じく ARM ARM に、「SMC 例外ハンドラ (セキュアモニタコード) で、要求されているサービスを特定するために使用できますが、この方法は非推奨です」とあります。

BootROM コードの L2 キャッシュ invalidate サービスは、r12=1 によってサービスを特定しているので、SMC に与える即値引数は何でもよいはずなので、とりあえず 0 を指定しておけばよいと思います。

.arch_extension sec は、コンパイルエラーを避けるために入れてあります。

これがないと、"Error: selected processor does not support ARM mode `smc #0" というコンパイルエラーが出てしまいます。

L2 キャッシュに関しては、このように BootROM の invalidate サービスを利用して invalidate してやればよいでしょう。

ちなみに、、、

xloader でも、あまり意味があるとは思えませんが、初期化時に L2 キャッシュの invalidate をしています。

以下のようなコードです。

0xE1600070 が、"smc #0" に相当するマシン語なんですね。

話を戻しまして、、、

L2 キャッシュの invalidate が必要なことは分かりました。

ただ、L1 キャッシュの invalidate が必要かどうかは、よく分かりません。

パワーオンリセット時は、L1 キャッシュは空でしょうから invalidate は必要ないでしょうが、パワーオンリセットでないリセット時は、リセットによってキャッシュが空になるかどうかは、ARM ARM にも Cortex-A8 TRM にも記述がないように思えます。(ただし、見落している可能性もあり。)

念のため、L1 キャッシュも invalidate しておいた方が確実と思います。

それでは、L1 命令キャッシュ、L1 データキャッシュ、L2 統一キャッシュをどのような手順で有効化するかというと、

・L1 命令キャッシュをすべて invalidate する

・L1 データキャッシュをすべて invalidate する

・L2 統一キャッシュをすべて invalidate する

・Control Register の I ビットを立てて L1 命令キャッシュを有効化する

・MMU を有効化する

- ページテーブルを構成する

- Translation Table Base Register にページテーブル先頭アドレスを設定する

- Control Register の M ビットを立てて MMU を有効化する

・Auxiliary Control Register の L2EN ビットを立てる

・Control Register の C ビットを立てて、L1 データキャッシュ、L2 統一キャッシュを有効化する

という方法でいいと思います。

分岐予測を有効にする場合は、更に以下を行います:

・分岐予測器を invalidate する

・Control Register の Z ビットを立てて分岐予測を有効化する

分岐予測器を invalidate するのは、ARM ARM に、「MMU の稼動または非稼動時に分岐予測器を無効化せよ」と書いてあるので (B2.2.6 分岐予測器 分岐予測器の保守操作とメモリオーダモデル)、それに従っています。

ところが、ずっと後で触れますが、Cortex-A8 においては、分岐予測器の invalidate は不要かもしれません。

キャッシュ無効化方法

キャッシュを無効にする場合、単にキャッシュ有効化ビットを落とせばいいわけではありません。

キャッシュを無効にすると同時に、キャッシュを clean しておく必要があります。

キャッシュ clean とは、キャッシュからメインメモリに排出させる動作のことを意味します。

キャッシュ clean を行わずにキャッシュを無効化すると、それまで書き込んできたデータの一部がキャッシュに残ってしまい、メインメモリが不完全な状態になってしまいます。

それでは、キャッシュ無効化とキャッシュ clean の順番はどうすればいいでしょうか。

キャッシュを無効化した後に、キャッシュを clean すればいいでしょうか。

それとも、キャッシュを clean した後にキャッシュを無効化すればいいでしょうか。

Cortex-A8 TRM には、キャッシュを無効化する前にキャッシュを clean および invalidate せよ、と書いてあります (7.2.3 Cache disabled behavior)。

キャッシュを無効化した後でも、キャッシュ保守命令(キャッシュ invalidate とか clean とか、キャッシュに作用する命令のこと)は有効であるとも書かれている (同じく 7.2.3 Cache disabled behavior) ので、逆順にしてもいいような気もしますが、TRM の記述に敢えて逆らう必要もないでしょう。

invalidate が必要な理由は、後でキャッシュを有効にするときに、キャッシュに残っているゴミデータがメインメモリに排出されてしまうことを防ぐためです。

もっとも、有効化する前にキャッシュ invalidate を行うようになっているならば、ここで invalidate する必要はありません。

キャッシュを clean および invalidate し始めてからキャッシュ有効化ビットを落とすまでの間、メモリには書き込みアクセスをしないようにしなければなりません。

さもないと、clean および invalidate した後のキャッシュに、メモリへの書き込みが滞留してしまう可能性があり、そうなると、その書き込みがメインメモリに届かなくなってしまいます。

これを防ぐには、キャッシュの clean および invalidate, キャッシュの無効化をするコードを、すべてアセンブリコードで書く必要があります。

例えば、C 言語で次のようにやるのはダメです:

clean_and_invalidate_cache();

disable_cache();

C 言語の呼び出しには、スタックの push/pop がつきものですので、clean_and_invalidate_cache() で全キャッシュを clean および invalidate した後、clean_and_invalidate_cache() から戻り、disable_cache() を呼び出した時に、disable_cache() の先頭でスタックへ push してしまうので、このスタックへの push 分がキャッシュに滞留してしまうのです。

また、clean_and_invalidate_cache() や disable_cache() で使われる関数オート変数への書き込みも、キャッシュに滞留してしまう可能性があります。

スタックへの push とか関数オート変数分くらい失われてもいいよ、というのであれば、以下のようにすれば大丈夫です。

clean_and_invalidate_cache();

disable_cache();

invalidate_cache();

これにより、clean_and_invdalidate_cache(), disable_cache() 内で行われるスタックへの push とかオート変数への書き込み以外は、すべてメインメモリに排出された上で、キャッシュが空になります。

最後に invalidate_cache() を呼び出しているのは、clean_and_invdalidate_cache(), disable_cache() 呼び出しでキャッシュに滞留してしまったデータ(スタックへの push 分とかオート変数への書き込み分とか)が、ゴミとして残らないようにするためです。

(Cortex-A8 TRM には、キャッシュ無効時でもキャッシュ保守命令は実行されると書いてあります。 7.2.3 Cache disabled behavior)

キャッシュの clean や invalidate は、近い方から行う方がいいのでしょうか、遠い方から行う方がいいのでしょうか。

言い換えると、L1 キャッシュを clean, invalidate してから、その後で L2 キャッシュを clean, invalidate すべきなのか、それとも逆なのか。

これは、やり方によって、状況が変わります。

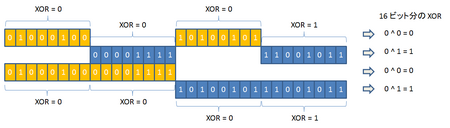

例えば、以下の方法では、clean & invalidate は、L1 キャッシュから L2 キャッシュへと行わなければなりません。

1. L1 データキャッシュを clean & invalidate

2. L2 キャッシュを clean & invalidate

3. Control Register の C ビットを落として L1 データキャッシュを無効化 (同時に L2 キャッシュも無効化される)

L2 キャッシュが有効な間は、L1 キャッシュの clean によるキャッシュデータの排出は、L2 キャッシュに行きます (Cortex-A8 TRM 8.3 Enabling and disabling the L2 cache controller の Note 参照) ので、1 と 2 の順番を入れ替えてしまうと、L2 キャッシュにデータが滞留してしまいます。

しかし、以下のように、clean & invalidate を、L2 キャッシュから行っても問題ないケースもあります。

1. L2 キャッシュを clean & invalidate

2. Auxiliary Control Register の L2EN ビットを落として L2 キャッシュを無効化

3. L1 データキャッシュを clean & invalidate

4. Control Register の C ビットを落として L1 データキャッシュを無効化

L2 キャッシュが無効になると、L1 キャッシュの clean によるキャッシュデータの排出は、メインメモリに行きますので (同じく Cortex-A8 TRM 8.3 Enabling and disabling the L2 cache controller の Note 参照)、3 の clean は、メインメモリに行くことになり、L2 キャッシュにデータが滞留してしまうことはないのです。

なお、L1 とか L2 とかを意識しなければならないのは、キャッシュレベル、セット、ウェイを指定して clean, invalidate する場合だけです。

アドレスを指定して clean, invalidate を行う場合には、上のようなことは意識する必要はありません。 (ただし、PoC まで clean, invalidate する必要があります。PoC については、後で触れます。)

以上で、キャッシュの有効化・無効化の説明はおしまいです。

有効、無効にするだけなのに、意外とめんどくさいです。

キャッシュ保守命令

キャッシュ保守命令について、もう少し見ていきましょう。

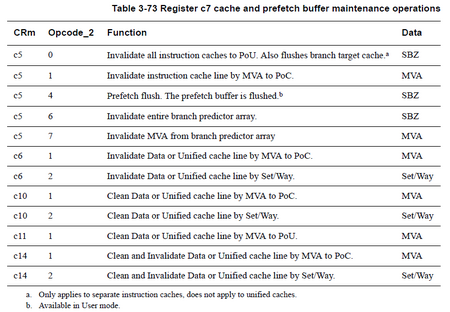

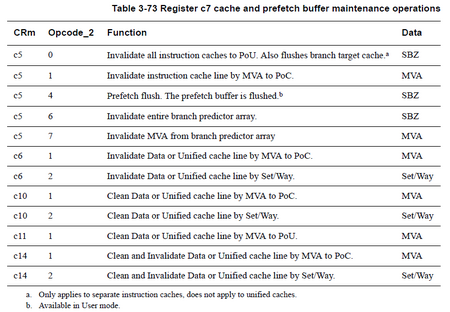

Cortex-A8 TRM に、キャッシュ保守命令の説明が載っています。

キャッシュ保守命令とは、clean, invalidate, clean and invalidate をキャッシュに対して行う命令です。clean は L1 データキャッシュ、L2 統一キャッシュに対して行うことが出来ますが、L1 命令キャッシュに対しては行うことはできません。

invalidate は、L1 命令キャッシュ、L1 データキャッシュ、L2 統一キャッシュに対して行うことができます。

キャッシュ保守命令は、cp15 コプロセッサーに対する命令という形で発行します。

cp15 コプロセッサーに対する命令は、MCR/MRC 命令を使います。

(実装上は、アセンブリ言語で記述する必要があります。)

例えば、以下は命令キャッシュと分岐予測器のキャッシュをすべて invalidate する命令です。

MCR p15, 0, <Rd>, c7, c5, 0

<Rd> には、汎用レジスタを指定します。

保守命令の対象キャッシュを、<Rd> で指定したレジスタの値で決定します。

上例では、'c5, 0' が「すべての命令キャッシュと分岐予測器のキャッシュ」を対象にしていることを意味するので、<Rd> は特定のキャッシュを指定する必要はなく、任意の値で良さそうに思えますが、実際には、値を 0 にしておかないといけません。(Cortex-A8 TRM Table 3-73 Register c7 cache and prefetch buffer maintenance operations)

<Rd> の次の c7 は、キャッシュ保守系列の命令であることを表します。

最後の 'c5, 0' が、保守命令の種類を表します。

その種類によって、<Rd> に設定する値のフォーマットが変わってきます。

以下は、Cortex-A8 TRM から抜粋したキャッシュ保守命令一覧です。

CRm と Opcode_2 が、上例でいうところの 'c5, 0' に相当します。

Data が <Rd> に相当します。

キャッシュ保守命令は、どのキャッシュを対象にするかについて、2 種類の指定方法を用意しています。

一つは、キャッシュレベル、セット番号、ウェイ番号を指定する方法で、もう一つは、MVA (= Modified Virtual Address) を指定する方法です。

MVA は、FCSE (= Fast Context Switch Extension) を使わなければ、仮想アドレスと一致するような、アドレス値です。

(多分、普通は FCSE を使わない、Linux でも多分使っていない)

MVA を指定するキャッシュ保守命令を実行すると、指定された MVA に対応するキャッシュラインに対して作用します。

仮に、指定された MVA に対応するキャッシュラインが存在しない場合は、空振りに終わるものと思います。

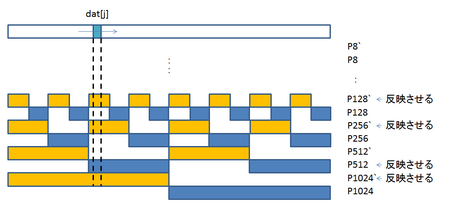

MVA を指定するキャッシュ保守命令には、PoC とか PoU とかいう言葉がついて回ります。

PoC まで命令キャッシュを invalidate するとか、PoU までデータキャッシュ/統一キャッシュを clean するとか、そんな感じです。

PoC = Point of Coherency, PoU = Point of Unification の略なのですが、その意味はというと、ARM ARM を見ても、今一つピンときません。

そこで、より明確に書きます。

PoC とは、具体的にはメインメモリを指します。

・PoC まで命令キャッシュを invalidate するということは、MVA に対応する L1 命令キャッシュ/L2 統一キャッシュを invalidate することを意味します。

・PoC までデータキャッシュ/統一キャッシュを clean するということは、MVA に対応する L1 データキャッシュ/L2 統一キャッシュを clean するということを意味します。

・また、PoC までデータキャッシュ/統一キャッシュを invalidate すると、MVA に対応する L1 データキャッシュ/L2 統一キャッシュが invalidate されます。

PoU とは、具体的には L2 統一キャッシュを指すと思います。

・PoU まで命令キャッシュを invalidate するということは、MVA に対応する L1 命令キャッシュを invalidate することを意味します。

・PoU までデータキャッシュ/統一キャッシュを clean するということは、MVA に対応する L1 データキャッシュを clean することを意味します。

・また、PoU までデータキャッシュ/統一キャッシュを invalidate すると、MVA に対応する L1 データキャッシュが invalidate されます。

※PoU までの invalidate/clean は、L2 統一キャッシュに作用しない。

PoC、PoU をさらに理解するにあたって、メモリにアクセスするエージェントの観点から見てみると、

1. 命令キャッシュ

2. データキャッシュ

3. 変換テーブルウォーク機構

4. その他、外部デバイス (DMA とか)

PoC まで命令キャッシュを invalidate し、かつ PoC までデータキャッシュ/統一キャッシュを clean すると、上記登場人物がすべて同じ値を見ることができるようになります。

PoU まで命令キャッシュを invalidate し、データキャッシュ/統一キャッシュを clean すると、「4. その他、外部デバイス」以外の 3者が、同じ値を見ることができるようになります。

ところで、、、

MCR p15, 0, <Rd>, c7, c5, 1 という命令は、"Invalidate instruction cache line by MVA" という意味の命令なのですが、これが PoU まで作用するのか、PoC まで作用するのか、Cortex-A8 TRM を見る限りでは判然としません。

"Table 3.73. Register c7 cache and prefetch buffer maintenance operations" には "Invalidate instruction cache line by MVA to PoC" と書いてあるのですが、"Table 16-13 Nonpipelined CP15 instructions" には、"Invalidate I$ Line by MVA to PoU" と書いてあります。

うーん・・・。

ウェブで Cortex-A15 の TRM を見てみると、MCR p15, 0, <Rd>, c7, c5, 1 は "Invalidate instruction caches by MVA to PoU" となっていますし、ARM ARM の「表 B3-32 CP15 c7 のキャッシュおよび分岐予測器の保守操作」を見てみても、「PoU まで、MVA によって命令キャッシュラインを無効化します」と書いてありますので、Cortex-A8 TRM の "Table 3.73. Register c7 cache and prefetch buffer maintenance operations" の "Invalidate instruction cache line by MVA to PoC" が、多分間違いですね。

PoU が正解と思います。

・・・

キャッシュの保守は、どのような時に実行する必要があるのでしょうか。

命令キャッシュ、データキャッシュ、統一キャッシュそれぞれについて見てみましょう。

命令キャッシュの invalidate が必要な時(ARM ARM B3.4.1 命令キャッシュの要件より)

a1. 命令アドレスへの新しいデータの書き込み

a2. 変換テーブルへの新しいアドレスマッピングの書き込み (注)

a3. ASID に影響を与えない TTBR0, TTBR1, TTBCR レジスタの変更 (注)

a4. SCTRL への書き込みによる MMU の許可または禁止 (注)

ARM7 アーキテクチャのオプション拡張機能の IVIPT 拡張機能(命令キャッシュの仮想インデクス物理タグ付き拡張機能)が実装されていれば、(注) がついている項目は、不要です。

Cortex-A8 は、IVIPT が実装されているので、(注) を付けた a2 - a4 は不要ということになります。

分岐予測器の invalidate が必要な時(ARM ARM B2.2.6 分岐予測器 分岐予測器の保守操作とメモリオーダモデルより)

b1. MMU の稼動または非稼動

b2. 命令位置への新しいデータの書き込み (注)

b3. 変換テーブルへの新しいマッピングの書き込み (注)

Cortex-A8 TRM を見ると、"Processor does not require flushing BTB on VA change." とあります (Table 3-21 Memory Model Feature Register 1 bit functions より)。

BTB は、Branch Target Buffer のことです。

また、"The BTB does not have to be invalidated on a context switch, self-modifying code, or any other change in the VA-to-PA mapping." ともあります。(5.6 Operating system and predictor context より)

これを見る限り、Cortex-A8 では、(注) を付けた b2 や、b3 を行ったとしても、分岐予測器の invalidate は必要ないということですね。

「b1. MMU の稼動または非稼動時」については何も書かれていないのですが、これも必要ないのかもしれません。

Cortex-A8 においては、分岐予測器の invalidate 命令、

MCR p15, 0, <Rd>, c7, c5, 6

MCR p15, 0, <Rd>, c7, c5, 7

は、デフォルトでは NOP と等価であるということが Cortex-A8 TRM に書いてあります。(3.1 About the system control coprosessor)

Auxiliary Control Register の IBE ビットを立てれば、これらの命令は分岐予測器の invalidate 命令として機能するようになります。

ですが、かといって、MMU の稼働または非稼働の時だけ IBE ビットを立てて invalidate を行わなければいけないとすると、不自然な気がします。

なので、MMU の稼動または非稼動時にも、分岐予測器の invalidate は不要なのではないかと・・・。

ただ、IBE ビットを立てない限り NOP と等価なわけですし、しかもサイクルペナルティを伴わない NOP とのことですし、Cortex-A8 に限定せず、ARM v7 アーキテクチャ全般で使用できるコードにしておいた方がいいと思いますので、b1, b2, b3 を行った際には、分岐予測器の invalidate 命令、MCR p15, 0, <Rd>, c7, c5, 6 / MCR p15, 0, <Rd>, c7, c5, 7 を入れておいた方がいいと思います。

データキャッシュの clean/invalidate が必要な時

ARM ARM には特に記載なし

それでは具体例として、コード領域を書き換えたときに必要なキャッシュ保守について、見てみましょう。

必要なのは、

- 命令キャッシュの invalidate

- 分岐予測器の invalidate

- データキャッシュの clean

です。

命令キャッシュの invalidate, 分岐予測器の invalidate は、上記命令キャッシュ・分岐予測器の invalidate 要件より、必要であることが分かります。

分岐予測器の invalidate は、Cortex-A8 では必要ありません。

必要ないのですが、先述したように ARM v7 アーキテクチャ全般で使えるコードにするために、入れておいた方がいいと思います。

データキャッシュの clean は、書き換えたコードデータが、データキャッシュに滞留することを防ぐために必要です。

データキャッシュの clean を行う際、書き換えた範囲だけ、PoU まで clean すれば OK です。

PoC まで clean しても特に問題ありませんが、PoU までで十分です。

実際の実装では、上記キャッシュ保守操作に併せて、メモリバリアを使う必要があります。

メモリバリアについては、別途説明をします。

それぞれのキャッシュサイズは、コプロセッサー cp15 の Cache Size Identification Register を読み出すことにより、知ることができます。

cp15 のレジスタには、mrc, mcr 命令でアクセスすることができます。

Cache Size Identification Register からは、キャッシュに関するサイズ以外の属性も読み出すことが出来ます。

beagleboard で実際に読み出してみると、以下のようになりました:

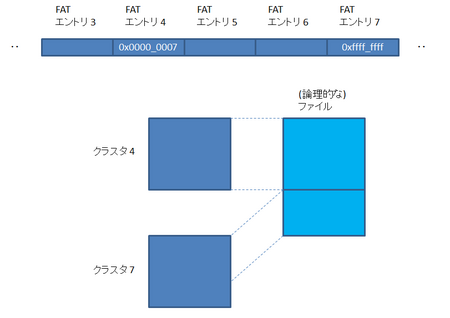

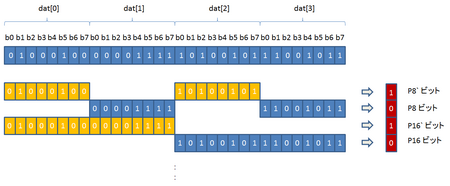

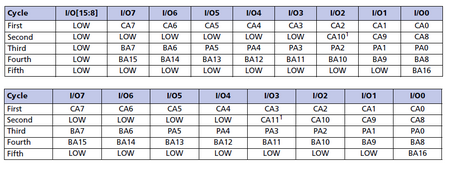

| WT | WB | RA | WA | セット数 | ウェイ数 | ラインサイズ | キャッシュサイズ | |

| L1命令キャッシュ | N | N | Y | N | 64 | 4 | 64 | 16384 |

| L1データキャッシュ | Y | Y | Y | N | 64 | 4 | 64 | 16384 |

| L2キャッシュ | Y | Y | Y | Y | 512 | 8 | 64 | 262144 |

WT = Write Through サポート

WB = Write Back サポート

RA = Read Allocation サポート

WA = Write Allocation サポート

キャッシュサイズは、セット数 * ウェイ数 * ラインサイズ により算出されます。

例えば L1 命令キャッシュの場合、64 * 4 * 64 = 16384 バイトです。

キャッシュを有効にする方法は、命令キャッシュとデータキャッシュ・統一キャッシュで異なります。

基本的には、Control Register の I ビット、C ビット、Auxiliary Control Register の L2EN ビットが有効/無効を決定するのですが。

命令キャッシュは、I ビットを立てるだけで有効化することができます。

しかし、データキャッシュ・統一キャッシュは、C ビット/L2EN ビットを立てるだけでは有効化できません。

C ビット/L2EN ビットを立てるとともに、MMU も有効にしてやる必要があります。

キャッシュの有効・無効は、次のようなルールに従います:

MMU 稼働の場合

- L1 命令キャッシュは、SCTRL.I ビットの 1/0 によって有効/無効が決まる

- L1 データキャッシュは、SCTRL.C ビットの 1/0 によって有効/無効が決まる

- L2 統一キャッシュは、SCTRL.C ビットが 1 かつ Auxiliary SCTRL.L2EN ビットが 1 の場合は有効、それ以外の組み合わせの場合は無効

MMU 非稼働の場合

- L1 命令キャッシュは、SCTRL.I ビットの 1/0 によって有効/無効が決まる

- L1 データキャッシュは、SCTRL.C ビットの 1/0 によらず、無効になる

- L2 統一キャッシュは、SCTRL.C ビットおよび Auxiliary SCTRL.L2EN ビットの 1/0 によらず、無効になる

※SCTRL = Control Register, Auxiliary SCTRL = Auxiliary Control Register は、コプロセッサー cp15 のレジスタです。

L1 命令キャッシュは、簡単に有効にすることができますが、L1 データキャッシュ、L2 統一キャッシュは MMU を有効化しないと有効にできないので、多少面倒です。

なお、L2 を統一キャッシュと言っているのは、命令データとロード・ストアデータの両方を持つからです。

※

x-loader で、キャッシュはどうなっているかというと、、、

x-loader では、MMU を有効にしていませんので、L1 データキャッシュおよび L2 統一キャッシュは無効です。

L1 命令キャッシュは、有効にしています。

同時に、分岐予測も有効にしています。

MMU を有効にするには、ページテーブルが必要です。

一番簡単なページテーブルは、すべて 16MB のスーパーセクションで構成し、仮想アドレス=物理アドレスとなるようにする構成でしょう。

これだと、4GB のアドレス空間をカバーするのに必要なページテーブルのサイズは、1KB で済みます。

さて、それではこれから、キャッシュの有効化方法、無効化方法について、触れていきます。

きっちりやろうとすると、意外とめんどくさいです。

キャッシュ有効化方法

キャッシュを有効化するには、基本的にはキャッシュ有効化ビットを立てればいいのですが、その前にキャッシュを空にしておく必要があります。

さもないと、キャッシュ中のゴミが、キャッシュ有効後にメインメモリに排出されてしまいます。

キャッシュを空にする動作は invalidate と言いますが、invalidate をどのように行うかがキャッシュ有効化時の考慮点です。

そもそも、L1 キャッシュ、L2 キャッシュともに invalidate する必要があるのかどうか?という点から考えてみる必要があります。

そのために、まず、リセット時にキャッシュがどうなるか、知らなければなりません。

ARM ARM の「B2.2.2 キャッシュの動作 → リセット時のキャッシュの動作」を見てみると、

・すべてのキャッシュはリセット時に非稼働になります。

・実装では、特定のキャッシュ初期化ルーチンを使用して、キャッシュを稼働させる前にその記憶域アレイを無効にすることが必要な場合があります。必要な初期化ルーチンの詳細な形式は実装定義ですが、このルーチンはデバイスのドキュメントの一部として明示的に文書化する必要があります。

とあります。

「デバイスのドキュメント」に相当すると思われる Cortex-A8 TRM を見てみると、L1 キャッシュに関しては、特に初期化に関しての記述はありません。

また、L2 キャッシュに関しても、Auxiliary Control Register の L2EN ビットを立ててから、Control Register の C ビットを立てよ、との記述があるくらいです (8.3 Enabling and disabling the L2 cache controller)。

そこで、さらに OMAP35x TRM を見てみると、

・L2 キャッシュを使用するには、事前に L2 キャッシュのデータをすべて invalidate しなくてはならない

・BootROM コードに、L2 キャッシュを invalidate するサービスを用意しておくので、パワーオンリセット後、もしくはリセット後に呼びなさい

・そのサービスは、r12 レジスタに 1 をセットした状態で SMI 命令を発行すると呼び出すことができる

とあります (25.4.1 Booting Overview の Caution)。

SMI は、セキュアモニタ命令であり、BootROM コードで実装されている L2 キャッシュの invalidate サービスが、モニターモードで実装されているため、SMI 命令を実行する必要があります。

実際には、SMI 命令ではなく、SMC 命令を使用します。

実装コードは、以下のようなアセンブリコードになります:

__asm__ volatile(".arch_extension sec\n\t"

"mov r12,#1\n\t"

"smc #0\n":::"r12");

SMC 命令は、ARM ARM には、「SMC (以前の SMI)」 と記載されています。

SMC 命令は、即値引数を一つ取ります。

この即値引数に関しては、同じく ARM ARM に、「SMC 例外ハンドラ (セキュアモニタコード) で、要求されているサービスを特定するために使用できますが、この方法は非推奨です」とあります。

BootROM コードの L2 キャッシュ invalidate サービスは、r12=1 によってサービスを特定しているので、SMC に与える即値引数は何でもよいはずなので、とりあえず 0 を指定しておけばよいと思います。

.arch_extension sec は、コンパイルエラーを避けるために入れてあります。

これがないと、"Error: selected processor does not support ARM mode `smc #0" というコンパイルエラーが出てしまいます。

L2 キャッシュに関しては、このように BootROM の invalidate サービスを利用して invalidate してやればよいでしょう。

ちなみに、、、

xloader でも、あまり意味があるとは思えませんが、初期化時に L2 キャッシュの invalidate をしています。

以下のようなコードです。

231: mov r12, #0x1 @ set up to invalide L2

232: smi: .word 0xE1600070 @ Call SMI monitor

0xE1600070 が、"smc #0" に相当するマシン語なんですね。

話を戻しまして、、、

L2 キャッシュの invalidate が必要なことは分かりました。

ただ、L1 キャッシュの invalidate が必要かどうかは、よく分かりません。

パワーオンリセット時は、L1 キャッシュは空でしょうから invalidate は必要ないでしょうが、パワーオンリセットでないリセット時は、リセットによってキャッシュが空になるかどうかは、ARM ARM にも Cortex-A8 TRM にも記述がないように思えます。(ただし、見落している可能性もあり。)

念のため、L1 キャッシュも invalidate しておいた方が確実と思います。

それでは、L1 命令キャッシュ、L1 データキャッシュ、L2 統一キャッシュをどのような手順で有効化するかというと、

・L1 命令キャッシュをすべて invalidate する

・L1 データキャッシュをすべて invalidate する

・L2 統一キャッシュをすべて invalidate する

・Control Register の I ビットを立てて L1 命令キャッシュを有効化する

・MMU を有効化する

- ページテーブルを構成する

- Translation Table Base Register にページテーブル先頭アドレスを設定する

- Control Register の M ビットを立てて MMU を有効化する

・Auxiliary Control Register の L2EN ビットを立てる

・Control Register の C ビットを立てて、L1 データキャッシュ、L2 統一キャッシュを有効化する

という方法でいいと思います。

分岐予測を有効にする場合は、更に以下を行います:

・分岐予測器を invalidate する

・Control Register の Z ビットを立てて分岐予測を有効化する

分岐予測器を invalidate するのは、ARM ARM に、「MMU の稼動または非稼動時に分岐予測器を無効化せよ」と書いてあるので (B2.2.6 分岐予測器 分岐予測器の保守操作とメモリオーダモデル)、それに従っています。

ところが、ずっと後で触れますが、Cortex-A8 においては、分岐予測器の invalidate は不要かもしれません。

キャッシュ無効化方法

キャッシュを無効にする場合、単にキャッシュ有効化ビットを落とせばいいわけではありません。

キャッシュを無効にすると同時に、キャッシュを clean しておく必要があります。

キャッシュ clean とは、キャッシュからメインメモリに排出させる動作のことを意味します。

キャッシュ clean を行わずにキャッシュを無効化すると、それまで書き込んできたデータの一部がキャッシュに残ってしまい、メインメモリが不完全な状態になってしまいます。

それでは、キャッシュ無効化とキャッシュ clean の順番はどうすればいいでしょうか。

キャッシュを無効化した後に、キャッシュを clean すればいいでしょうか。

それとも、キャッシュを clean した後にキャッシュを無効化すればいいでしょうか。

Cortex-A8 TRM には、キャッシュを無効化する前にキャッシュを clean および invalidate せよ、と書いてあります (7.2.3 Cache disabled behavior)。

キャッシュを無効化した後でも、キャッシュ保守命令(キャッシュ invalidate とか clean とか、キャッシュに作用する命令のこと)は有効であるとも書かれている (同じく 7.2.3 Cache disabled behavior) ので、逆順にしてもいいような気もしますが、TRM の記述に敢えて逆らう必要もないでしょう。

invalidate が必要な理由は、後でキャッシュを有効にするときに、キャッシュに残っているゴミデータがメインメモリに排出されてしまうことを防ぐためです。

もっとも、有効化する前にキャッシュ invalidate を行うようになっているならば、ここで invalidate する必要はありません。

キャッシュを clean および invalidate し始めてからキャッシュ有効化ビットを落とすまでの間、メモリには書き込みアクセスをしないようにしなければなりません。

さもないと、clean および invalidate した後のキャッシュに、メモリへの書き込みが滞留してしまう可能性があり、そうなると、その書き込みがメインメモリに届かなくなってしまいます。

これを防ぐには、キャッシュの clean および invalidate, キャッシュの無効化をするコードを、すべてアセンブリコードで書く必要があります。

例えば、C 言語で次のようにやるのはダメです:

clean_and_invalidate_cache();

disable_cache();

C 言語の呼び出しには、スタックの push/pop がつきものですので、clean_and_invalidate_cache() で全キャッシュを clean および invalidate した後、clean_and_invalidate_cache() から戻り、disable_cache() を呼び出した時に、disable_cache() の先頭でスタックへ push してしまうので、このスタックへの push 分がキャッシュに滞留してしまうのです。

また、clean_and_invalidate_cache() や disable_cache() で使われる関数オート変数への書き込みも、キャッシュに滞留してしまう可能性があります。

スタックへの push とか関数オート変数分くらい失われてもいいよ、というのであれば、以下のようにすれば大丈夫です。

clean_and_invalidate_cache();

disable_cache();

invalidate_cache();

これにより、clean_and_invdalidate_cache(), disable_cache() 内で行われるスタックへの push とかオート変数への書き込み以外は、すべてメインメモリに排出された上で、キャッシュが空になります。

最後に invalidate_cache() を呼び出しているのは、clean_and_invdalidate_cache(), disable_cache() 呼び出しでキャッシュに滞留してしまったデータ(スタックへの push 分とかオート変数への書き込み分とか)が、ゴミとして残らないようにするためです。

(Cortex-A8 TRM には、キャッシュ無効時でもキャッシュ保守命令は実行されると書いてあります。 7.2.3 Cache disabled behavior)

キャッシュの clean や invalidate は、近い方から行う方がいいのでしょうか、遠い方から行う方がいいのでしょうか。

言い換えると、L1 キャッシュを clean, invalidate してから、その後で L2 キャッシュを clean, invalidate すべきなのか、それとも逆なのか。

これは、やり方によって、状況が変わります。

例えば、以下の方法では、clean & invalidate は、L1 キャッシュから L2 キャッシュへと行わなければなりません。

1. L1 データキャッシュを clean & invalidate

2. L2 キャッシュを clean & invalidate

3. Control Register の C ビットを落として L1 データキャッシュを無効化 (同時に L2 キャッシュも無効化される)

L2 キャッシュが有効な間は、L1 キャッシュの clean によるキャッシュデータの排出は、L2 キャッシュに行きます (Cortex-A8 TRM 8.3 Enabling and disabling the L2 cache controller の Note 参照) ので、1 と 2 の順番を入れ替えてしまうと、L2 キャッシュにデータが滞留してしまいます。

しかし、以下のように、clean & invalidate を、L2 キャッシュから行っても問題ないケースもあります。

1. L2 キャッシュを clean & invalidate

2. Auxiliary Control Register の L2EN ビットを落として L2 キャッシュを無効化

3. L1 データキャッシュを clean & invalidate

4. Control Register の C ビットを落として L1 データキャッシュを無効化

L2 キャッシュが無効になると、L1 キャッシュの clean によるキャッシュデータの排出は、メインメモリに行きますので (同じく Cortex-A8 TRM 8.3 Enabling and disabling the L2 cache controller の Note 参照)、3 の clean は、メインメモリに行くことになり、L2 キャッシュにデータが滞留してしまうことはないのです。

なお、L1 とか L2 とかを意識しなければならないのは、キャッシュレベル、セット、ウェイを指定して clean, invalidate する場合だけです。

アドレスを指定して clean, invalidate を行う場合には、上のようなことは意識する必要はありません。 (ただし、PoC まで clean, invalidate する必要があります。PoC については、後で触れます。)

以上で、キャッシュの有効化・無効化の説明はおしまいです。

有効、無効にするだけなのに、意外とめんどくさいです。

キャッシュ保守命令

キャッシュ保守命令について、もう少し見ていきましょう。

Cortex-A8 TRM に、キャッシュ保守命令の説明が載っています。

キャッシュ保守命令とは、clean, invalidate, clean and invalidate をキャッシュに対して行う命令です。clean は L1 データキャッシュ、L2 統一キャッシュに対して行うことが出来ますが、L1 命令キャッシュに対しては行うことはできません。

invalidate は、L1 命令キャッシュ、L1 データキャッシュ、L2 統一キャッシュに対して行うことができます。

キャッシュ保守命令は、cp15 コプロセッサーに対する命令という形で発行します。

cp15 コプロセッサーに対する命令は、MCR/MRC 命令を使います。

(実装上は、アセンブリ言語で記述する必要があります。)

例えば、以下は命令キャッシュと分岐予測器のキャッシュをすべて invalidate する命令です。

MCR p15, 0, <Rd>, c7, c5, 0

<Rd> には、汎用レジスタを指定します。

保守命令の対象キャッシュを、<Rd> で指定したレジスタの値で決定します。

上例では、'c5, 0' が「すべての命令キャッシュと分岐予測器のキャッシュ」を対象にしていることを意味するので、<Rd> は特定のキャッシュを指定する必要はなく、任意の値で良さそうに思えますが、実際には、値を 0 にしておかないといけません。(Cortex-A8 TRM Table 3-73 Register c7 cache and prefetch buffer maintenance operations)

<Rd> の次の c7 は、キャッシュ保守系列の命令であることを表します。

最後の 'c5, 0' が、保守命令の種類を表します。

その種類によって、<Rd> に設定する値のフォーマットが変わってきます。

以下は、Cortex-A8 TRM から抜粋したキャッシュ保守命令一覧です。

CRm と Opcode_2 が、上例でいうところの 'c5, 0' に相当します。

Data が <Rd> に相当します。

キャッシュ保守命令は、どのキャッシュを対象にするかについて、2 種類の指定方法を用意しています。

一つは、キャッシュレベル、セット番号、ウェイ番号を指定する方法で、もう一つは、MVA (= Modified Virtual Address) を指定する方法です。

MVA は、FCSE (= Fast Context Switch Extension) を使わなければ、仮想アドレスと一致するような、アドレス値です。

(多分、普通は FCSE を使わない、Linux でも多分使っていない)

MVA を指定するキャッシュ保守命令を実行すると、指定された MVA に対応するキャッシュラインに対して作用します。

仮に、指定された MVA に対応するキャッシュラインが存在しない場合は、空振りに終わるものと思います。

MVA を指定するキャッシュ保守命令には、PoC とか PoU とかいう言葉がついて回ります。

PoC まで命令キャッシュを invalidate するとか、PoU までデータキャッシュ/統一キャッシュを clean するとか、そんな感じです。

PoC = Point of Coherency, PoU = Point of Unification の略なのですが、その意味はというと、ARM ARM を見ても、今一つピンときません。

そこで、より明確に書きます。

PoC とは、具体的にはメインメモリを指します。

・PoC まで命令キャッシュを invalidate するということは、MVA に対応する L1 命令キャッシュ/L2 統一キャッシュを invalidate することを意味します。

・PoC までデータキャッシュ/統一キャッシュを clean するということは、MVA に対応する L1 データキャッシュ/L2 統一キャッシュを clean するということを意味します。

・また、PoC までデータキャッシュ/統一キャッシュを invalidate すると、MVA に対応する L1 データキャッシュ/L2 統一キャッシュが invalidate されます。

PoU とは、具体的には L2 統一キャッシュを指すと思います。

・PoU まで命令キャッシュを invalidate するということは、MVA に対応する L1 命令キャッシュを invalidate することを意味します。

・PoU までデータキャッシュ/統一キャッシュを clean するということは、MVA に対応する L1 データキャッシュを clean することを意味します。

・また、PoU までデータキャッシュ/統一キャッシュを invalidate すると、MVA に対応する L1 データキャッシュが invalidate されます。

※PoU までの invalidate/clean は、L2 統一キャッシュに作用しない。

PoC、PoU をさらに理解するにあたって、メモリにアクセスするエージェントの観点から見てみると、

1. 命令キャッシュ

2. データキャッシュ

3. 変換テーブルウォーク機構

4. その他、外部デバイス (DMA とか)

PoC まで命令キャッシュを invalidate し、かつ PoC までデータキャッシュ/統一キャッシュを clean すると、上記登場人物がすべて同じ値を見ることができるようになります。

PoU まで命令キャッシュを invalidate し、データキャッシュ/統一キャッシュを clean すると、「4. その他、外部デバイス」以外の 3者が、同じ値を見ることができるようになります。

ところで、、、

MCR p15, 0, <Rd>, c7, c5, 1 という命令は、"Invalidate instruction cache line by MVA" という意味の命令なのですが、これが PoU まで作用するのか、PoC まで作用するのか、Cortex-A8 TRM を見る限りでは判然としません。

"Table 3.73. Register c7 cache and prefetch buffer maintenance operations" には "Invalidate instruction cache line by MVA to PoC" と書いてあるのですが、"Table 16-13 Nonpipelined CP15 instructions" には、"Invalidate I$ Line by MVA to PoU" と書いてあります。

うーん・・・。

ウェブで Cortex-A15 の TRM を見てみると、MCR p15, 0, <Rd>, c7, c5, 1 は "Invalidate instruction caches by MVA to PoU" となっていますし、ARM ARM の「表 B3-32 CP15 c7 のキャッシュおよび分岐予測器の保守操作」を見てみても、「PoU まで、MVA によって命令キャッシュラインを無効化します」と書いてありますので、Cortex-A8 TRM の "Table 3.73. Register c7 cache and prefetch buffer maintenance operations" の "Invalidate instruction cache line by MVA to PoC" が、多分間違いですね。

PoU が正解と思います。

・・・

キャッシュの保守は、どのような時に実行する必要があるのでしょうか。

命令キャッシュ、データキャッシュ、統一キャッシュそれぞれについて見てみましょう。

命令キャッシュの invalidate が必要な時(ARM ARM B3.4.1 命令キャッシュの要件より)

a1. 命令アドレスへの新しいデータの書き込み

a2. 変換テーブルへの新しいアドレスマッピングの書き込み (注)

a3. ASID に影響を与えない TTBR0, TTBR1, TTBCR レジスタの変更 (注)

a4. SCTRL への書き込みによる MMU の許可または禁止 (注)

ARM7 アーキテクチャのオプション拡張機能の IVIPT 拡張機能(命令キャッシュの仮想インデクス物理タグ付き拡張機能)が実装されていれば、(注) がついている項目は、不要です。

Cortex-A8 は、IVIPT が実装されているので、(注) を付けた a2 - a4 は不要ということになります。

分岐予測器の invalidate が必要な時(ARM ARM B2.2.6 分岐予測器 分岐予測器の保守操作とメモリオーダモデルより)

b1. MMU の稼動または非稼動

b2. 命令位置への新しいデータの書き込み (注)

b3. 変換テーブルへの新しいマッピングの書き込み (注)

Cortex-A8 TRM を見ると、"Processor does not require flushing BTB on VA change." とあります (Table 3-21 Memory Model Feature Register 1 bit functions より)。

BTB は、Branch Target Buffer のことです。

また、"The BTB does not have to be invalidated on a context switch, self-modifying code, or any other change in the VA-to-PA mapping." ともあります。(5.6 Operating system and predictor context より)

これを見る限り、Cortex-A8 では、(注) を付けた b2 や、b3 を行ったとしても、分岐予測器の invalidate は必要ないということですね。

「b1. MMU の稼動または非稼動時」については何も書かれていないのですが、これも必要ないのかもしれません。

Cortex-A8 においては、分岐予測器の invalidate 命令、

MCR p15, 0, <Rd>, c7, c5, 6

MCR p15, 0, <Rd>, c7, c5, 7

は、デフォルトでは NOP と等価であるということが Cortex-A8 TRM に書いてあります。(3.1 About the system control coprosessor)

Auxiliary Control Register の IBE ビットを立てれば、これらの命令は分岐予測器の invalidate 命令として機能するようになります。

ですが、かといって、MMU の稼働または非稼働の時だけ IBE ビットを立てて invalidate を行わなければいけないとすると、不自然な気がします。

なので、MMU の稼動または非稼動時にも、分岐予測器の invalidate は不要なのではないかと・・・。

ただ、IBE ビットを立てない限り NOP と等価なわけですし、しかもサイクルペナルティを伴わない NOP とのことですし、Cortex-A8 に限定せず、ARM v7 アーキテクチャ全般で使用できるコードにしておいた方がいいと思いますので、b1, b2, b3 を行った際には、分岐予測器の invalidate 命令、MCR p15, 0, <Rd>, c7, c5, 6 / MCR p15, 0, <Rd>, c7, c5, 7 を入れておいた方がいいと思います。

データキャッシュの clean/invalidate が必要な時

ARM ARM には特に記載なし

それでは具体例として、コード領域を書き換えたときに必要なキャッシュ保守について、見てみましょう。

必要なのは、

- 命令キャッシュの invalidate

- 分岐予測器の invalidate

- データキャッシュの clean

です。

命令キャッシュの invalidate, 分岐予測器の invalidate は、上記命令キャッシュ・分岐予測器の invalidate 要件より、必要であることが分かります。

分岐予測器の invalidate は、Cortex-A8 では必要ありません。

必要ないのですが、先述したように ARM v7 アーキテクチャ全般で使えるコードにするために、入れておいた方がいいと思います。

データキャッシュの clean は、書き換えたコードデータが、データキャッシュに滞留することを防ぐために必要です。

データキャッシュの clean を行う際、書き換えた範囲だけ、PoU まで clean すれば OK です。

PoC まで clean しても特に問題ありませんが、PoU までで十分です。

実際の実装では、上記キャッシュ保守操作に併せて、メモリバリアを使う必要があります。

メモリバリアについては、別途説明をします。

beagleboard を触ろう - Windows 開発環境 [組み込みソフト]

x-loader は、cygwin 環境でもビルドすることができます。

やっぱり、Windows だと何かと便利なので、cygwin 上での開発環境を作ってしまいましょう。

http://www.codesourcery.com/sgpp/lite/arm/portal/subscription?@template=lite

から、Windows 用バイナリを取得します。

このページの、Target OS が GNU/Linux の All versions... をクリックすると、

https://sourcery.mentor.com/sgpp/lite/arm/portal/subscription3057

に行きます。

Sourcery G++ Lite の最新版を取得しましょう。

私が見たときは、Sourcery G++ Lite 2011.03-41 が最新でした。

そこをクリックすると、

https://sourcery.mentor.com/sgpp/lite/arm/portal/release1803

に行きます。

ここで、IA32 Windows INSTALLER をクリックして、インストーライメージを保存・実行もしくは直接実行します。

デフォルトでは C:\Program Files 以下にインストールされてしまいますが、cygwin 環境では空白文字入りのファイル名は不便なので、インストール先を変更します。

私は、C:\cygwin\opt\sourcery にしました。

インストールが完了したら、パスを通します。

PATH 環境変数に、C:\cygwin\opt\sourcery\bin を追加です。

それではビルドですが、ソースコードを取ってきて、以下を cygwin から実行です。

・export CYGPATH=c:/cygwin/bin/cygpath.exe

・tar zxf xloader_xxx.tar.gz

・cd xloader

・make omap3530beagle_config

・make

・./signGP.exe x-load.bin

・cp x-load.bin.ift MLO

・MLO を SD カードにコピー

cygwin でビルドできるようにするために、config.mk を 1箇所だけ変更してあります:

gccincdir := $(shell $(CC) -print-file-name=include)

⇒ gccincdir := $(shell $(CC) -print-file-name=include | sed -e "s/^c:/\/cygdrive\/c/")

これをやっておかないと、make の際にエラーが出てしまいます。

make 実行時に .depend が作られますが、↑の修正をやらないと、.depend は、以下のようになってしまいます。

:

omap3530beagle.o: omap3530beagle.c \

/cygdrive/c/work/beagleboard/xloader/include/common.h \

/cygdrive/c/work/beagleboard/xloader/include/config.h \

/cygdrive/c/work/beagleboard/xloader/include/configs/omap3530beagle.h \

/cygdrive/c/work/beagleboard/xloader/include/asm/arch/cpu.h \

/cygdrive/c/work/beagleboard/xloader/include/asm/arch/omap3430.h \

/cygdrive/c/work/beagleboard/xloader/include/asm/arch/sizes.h \

/cygdrive/c/work/beagleboard/xloader/include/linux/types.h \

/cygdrive/c/work/beagleboard/xloader/include/linux/config.h \

/cygdrive/c/work/beagleboard/xloader/include/linux/posix_types.h \

/cygdrive/c/work/beagleboard/xloader/include/linux/stddef.h \

/cygdrive/c/work/beagleboard/xloader/include/asm/posix_types.h \

/cygdrive/c/work/beagleboard/xloader/include/asm/types.h \

c:/cygwin/opt/sourcery/bin/../lib/gcc/arm-none-linux-gnueabi/4.5.2/include/stdarg.h \

:

c:/cygwin/opt/sourcery/... の行が不正で、make がエラーになってしまいます。

c:/cygwin/opt/sourcery/... → /cygdrive/c/cygwin/opt/sourcery/...

と変更するための修正が、sed -e "s/^c:/\/cygdrive\/c/" の追加です。

cygwin を C ドライブ以外にインストールされている方は、sed -e... 以下を適当に変更してください。

・・・

これで、cygwin 上でビルドできるようになりました。

ソースコードのページ

やっぱり、Windows だと何かと便利なので、cygwin 上での開発環境を作ってしまいましょう。

http://www.codesourcery.com/sgpp/lite/arm/portal/subscription?@template=lite

から、Windows 用バイナリを取得します。

このページの、Target OS が GNU/Linux の All versions... をクリックすると、

https://sourcery.mentor.com/sgpp/lite/arm/portal/subscription3057

に行きます。

Sourcery G++ Lite の最新版を取得しましょう。

私が見たときは、Sourcery G++ Lite 2011.03-41 が最新でした。

そこをクリックすると、

https://sourcery.mentor.com/sgpp/lite/arm/portal/release1803

に行きます。

ここで、IA32 Windows INSTALLER をクリックして、インストーライメージを保存・実行もしくは直接実行します。

デフォルトでは C:\Program Files 以下にインストールされてしまいますが、cygwin 環境では空白文字入りのファイル名は不便なので、インストール先を変更します。

私は、C:\cygwin\opt\sourcery にしました。

インストールが完了したら、パスを通します。

PATH 環境変数に、C:\cygwin\opt\sourcery\bin を追加です。

それではビルドですが、ソースコードを取ってきて、以下を cygwin から実行です。

・export CYGPATH=c:/cygwin/bin/cygpath.exe

・tar zxf xloader_xxx.tar.gz

・cd xloader

・make omap3530beagle_config

・make

・./signGP.exe x-load.bin

・cp x-load.bin.ift MLO

・MLO を SD カードにコピー

cygwin でビルドできるようにするために、config.mk を 1箇所だけ変更してあります:

gccincdir := $(shell $(CC) -print-file-name=include)

⇒ gccincdir := $(shell $(CC) -print-file-name=include | sed -e "s/^c:/\/cygdrive\/c/")

これをやっておかないと、make の際にエラーが出てしまいます。

make 実行時に .depend が作られますが、↑の修正をやらないと、.depend は、以下のようになってしまいます。

:

omap3530beagle.o: omap3530beagle.c \

/cygdrive/c/work/beagleboard/xloader/include/common.h \

/cygdrive/c/work/beagleboard/xloader/include/config.h \

/cygdrive/c/work/beagleboard/xloader/include/configs/omap3530beagle.h \

/cygdrive/c/work/beagleboard/xloader/include/asm/arch/cpu.h \

/cygdrive/c/work/beagleboard/xloader/include/asm/arch/omap3430.h \

/cygdrive/c/work/beagleboard/xloader/include/asm/arch/sizes.h \

/cygdrive/c/work/beagleboard/xloader/include/linux/types.h \

/cygdrive/c/work/beagleboard/xloader/include/linux/config.h \

/cygdrive/c/work/beagleboard/xloader/include/linux/posix_types.h \

/cygdrive/c/work/beagleboard/xloader/include/linux/stddef.h \

/cygdrive/c/work/beagleboard/xloader/include/asm/posix_types.h \

/cygdrive/c/work/beagleboard/xloader/include/asm/types.h \

c:/cygwin/opt/sourcery/bin/../lib/gcc/arm-none-linux-gnueabi/4.5.2/include/stdarg.h \

:

c:/cygwin/opt/sourcery/... の行が不正で、make がエラーになってしまいます。

c:/cygwin/opt/sourcery/... → /cygdrive/c/cygwin/opt/sourcery/...

と変更するための修正が、sed -e "s/^c:/\/cygdrive\/c/" の追加です。

cygwin を C ドライブ以外にインストールされている方は、sed -e... 以下を適当に変更してください。

・・・

これで、cygwin 上でビルドできるようになりました。

ソースコードのページ

beagleboard を触ろう - ソースコード [組み込みソフト]

これまでの記事では、文章と絵とソースコードが少々という構成でしたが、ソースコード全体がありませんでした。

エッセンスだけ抽出して、できるだけ簡潔に、という記事を目指していたので、ソースコードなんて要らないだろうと思っていたのですが、、、

ひょっとしたら、自分の手元で動かして確かめてみたいという方がおられないとも限らないので、公開することにします。

公開するといっても、x-loader にちょろちょろと手を入れているだけのソースコードですが (^^;

これです↓

ソースコードのページ

ビルド方法については、「開発環境のインストール」「x-loader ビルド」「Windows 開発環境」の回の記事を参照してください。

CodeSourcery をインストールしてあれば、

・tar-ball を展開

・xloader ディレクトリができるので、そこに移動

・make omap3530beagle_config

・make

・./signGP x-load.bin

・cp x-load.bin.ift MLO

・MLO を SD カードにコピー

で OK です。

私がいつも使っている SD カードは、「angstrom ブート」の記事中の方法で作ったもので、FAT32 と ext3 が混在したものなのですが、多分、全体を FAT32 でフォーマットしたものでも大丈夫です。

MLO を、FAT32 領域にコピーしてください。

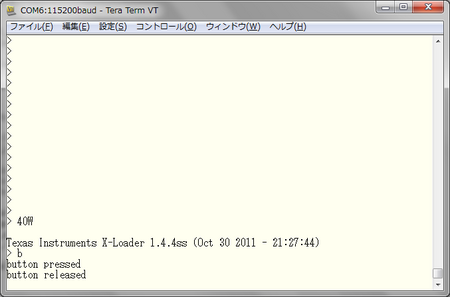

USER ボタンを押下しながら電源を入れると、beagleboard は SD カードから MLO (=x-loader) をロードして実行します。

PC 側のシリアル端末は、なんでもいいと思いますが、私は TeraTerm を使っています。

ボーレートは、115200 bps にしてください。

無事 x-loader が実行されると、コマンドプロンプトらしき '>' マークが表示されます。

このプロンプトでは、次のコマンドを受け付けます:

i : UART 割り込みテスト

d : UART DMA テスト

t : タイマーテスト

l : LED テスト

b : ボタンテスト

s : SDRAM テスト

n : NAND テスト

sd: SD カードテスト

m : DSS テスト

各テストの内容は、以下です。

UART 割り込みテスト

「UART 割り込みモード」の回に作ったものです。

UART3 を割り込みモードに設定し、'q' が入力されるまでループします。

1 秒おきに "uart_interrupt_test" という文字列をシリアルコンソールに表示します。

'q' 以外を入力すると、"OK" という文字列をシリアルコンソールに表示します。

'q' を入力するとコマンドプロンプトに戻ります。

UART DMA テスト

「UART DMA モード」の回に作ったものです。

UART3 を DMA モードに設定し、シリアルコンソールから 8 文字入力されるまで、ビジーループします。

UART3 に入力された 8 文字は、DMA によって dma_buf 上に転送されます。

転送された 8 文字をシリアルコンソールに出力した後、コマンドプロンプトに戻ります。

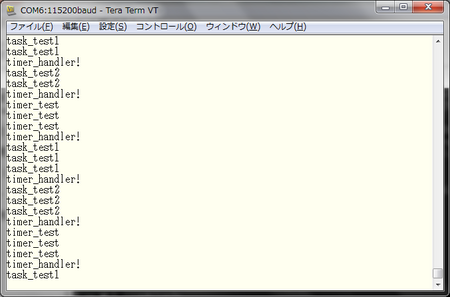

タイマーテスト

「タイマーとコンテキストスイッチ」の回に作ったものです。

タスクを 2 つ追加し、3 秒おきにコンテキストスイッチを行います。

'q' を入力するとコマンドプロンプトに戻ります。

ただし、'q' を入力しても、即座にはコマンドプロンプトには戻りません。

メインタスクに実行権が移った時、'q' が入力されたかどうかがチェックされます。

LED テスト

「LED とボタン」の回に作ったものです。

LED を点滅させます。

'q' を入力するとコマンドプロンプトに戻ります。

ボタンテスト

「LED とボタン」の回に作ったものです。

USER ボタンを押下すると、シリアルコンソールに "button pressed", "button released" を表示します。

'q' を入力するとコマンドプロンプトに戻ります。

SDRAM テスト

SDRAM の読み書きを全領域にわたって行います。

テストが完了すると、サイクルカウンターの値をシリアルコンソールに出力してコマンドプロンプトに戻ります。

NAND テスト

「メモリ」の回に作ったものです。

NAND テストは、以下の 4 つのテストから成ります:

ns: NAND ステータステスト

NAND ステータスを取得します。

ステータス取得後、コマンドプロンプトに戻ります。

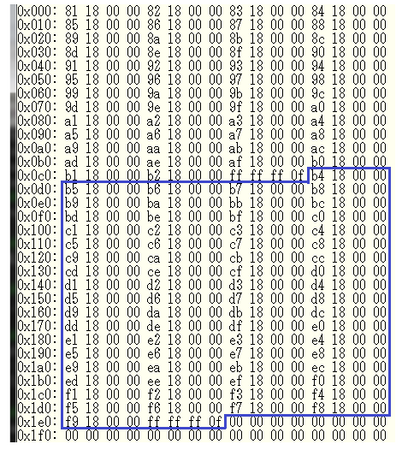

nr: NAND 読み出しテスト

オフセット 0x07FE0000 から 1 ページ読み出します。

これは、最も高位にあるページです。

読み出し先は、0x88000000 という SDRAM 上の適当なアドレスです。

読み出し完了後、読み出した値を表示して、コマンドプロンプトに戻ります。

ne: NAND 消去テスト

オフセット 0x07FE0000 からの 1 ページを消去します。

消去完了後、コマンドプロンプトに戻ります。

np: NAND プログラムテスト

2 つの引数、off と len を取ります(引き数 off は 1 桁の値のみ・・・)。

np 6 10 のように入力して引数を渡します。

オフセット 0x07FE0000 + off に 0x88000000 に書かれているデータを長さ len 分だけ書き込みます。

書き込み完了後、コマンドプロンプトに戻ります。

SD カードテスト

「FAT ファイルシステム」の回に作ったものです。

1 つの引き数 blknr を取ります。

sd 10 のように入力して引数を渡します。

SD カードから、ブロック番号 blknr から 1 ブロック分読み出します。

読み出した値をシリアルコンソールに出力した後、コマンドプロンプトに戻ります。

DSS テスト

「LCD 表示」「LCD 表示 (2)」の回に作ったものです。

このテストを試すには、HDMI-DVI 変換ケーブルで beagleboard と液晶ディスプレイを接続しておく必要があります。

DSS テストは、32 個のサブコマンドがあります。

'm' の後に、空白文字を 1 つ挟んで、サブコマンド番号を入力します。

m 0:

640 x 480 @ 60Hz で DSS を初期化します。

m 1:

640 x 480 @ 75Hz で DSS を初期化します。

m 2:

800 x 600 @ 60Hz で DSS を初期化します。

m 3:

1024 x 768 @ 60Hz で DSS を初期化します。

m 4:

1280 x 1024 @ 60Hz で DSS を初期化します。

m 5:

fuji.bgr を SD カードから読み出して、Video1 画面に表示します。

fuji.bgr は、640 x 512 サイズ、RGB24 フォーマット (データ並び順は BGR) の画像データです。

m 6:

Video1 画面を無効化します。

m 7:

Video2 画面を無効化します。

m 8:

Graphics 画面を無効化します。

m 9:

asa.bgr, cake.bgr, shin.bgr を SD カードから読み出して、それぞれ Video1 画面、Video2 画面、Graphics 画面に表示します。

asa.bgr, cake.bgr, shin.bgr は、いずれも 640 x 512 サイズ、RGB24 フォーマット (データ並び順は BGR) の画像データです。

画像の配置は、1280 x 1024 にちょうど収まるような配置にしています。

m 10:

asa.bgr, cake.bgr, shin.bgr を SD カードから読み出して、それぞれ Video1 画面、Video2 画面、Graphics 画面に表示します。

コマンド 9 と違って、重なり表示をするようにしています。

ついでに重なったまま動きます。

m 11:

fuji.bgr を SD カードから読み出して、Video1 画面に拡大表示します。

m 12:

fuji.bgr を SD カードから読み出して、Video1 画面に縮小表示します。

※ 1280 x 1024 でこれを実行すると、画面が乱れてしまいますので、1024 x 768 でお試しください。

m 13:

fuji.bgr を SD カードから読み出して、Video1 画面上で徐々に拡大させていきます。

m 14:

asa_a.bgr, cake_a.bgr, shin_a.bgr を SD カードから読み出して、それぞれ Video1 画面、Video2 画面、Graphics 画面に表示します。

asa_a.bgr, cake_a.bgr, shin_a.bgr は、いずれも 640 x 512 サイズ、ARGB32 フォーマット (データ並び順は BGRA) の画像データです。

アルファブレンドは、すべてのピクセルにおいて、50% (アルファ値としては 0x80) にしています。

画像の配置は、1280 x 1024 にちょうど収まるような配置にしています。

m 15:

asa_a.bgr, cake_a.bgr, shin_a.bgr を SD カードから読み出して、それぞれ Video1 画面、Video2 画面、Graphics 画面に表示します。

コマンド 14 と違って、重なり表示をするようにしています。

※ 1280 x 1024 でこれを実行すると、画面が乱れてしまいますので、1024 x 768 でお試しください。

m 16:

asa.bgr を SD カードから読み出して、Video2 画面に表示します。

m 17:

asa_a.bgr を SD カードから読み出して、Video2 画面に表示します。

m 18:

asa_a0.bgr を SD カードから読み出して、Video2 画面に表示します。

asa_a0.bgr は 640 x 512 サイズ、ARGB32 フォーマットの画像データ (データ並び順は BGRA) で、アルファブレンドはすべてのピクセルにおいて、100% (アルファ値としては 0x00)にしています。

アルファブレンドを有効にすると、asa_a0.bgr は透過率 100% となって表示されません。

m 19:

asa_aff.bgr を SD カードから読み出して、Video2 画面に表示します。

asa_aff.bgr は 640 x 512 サイズ、ARGB32 フォーマットの画像データ (データ並び順は BGRA) で、アルファブレンドはすべてのピクセルにおいて、0% (アルファ値としては 0xff)にしています。

m 20:

アルファブレンドを有効にし、Video2 画面、Graphics 画面のグローバルアルファブレンドを 0% (アルファ値としては 0xff) にします。

アルファブレンド 0% は、全く透過させないことを意味します。

コマンド 16 - 19 によって表示された画像は、画像データ中のアルファ値によってのみアルファブレンドが決定されます。

m 21:

アルファブレンドを有効にし、Video2 画面、Graphics 画面のグローバルアルファブレンドを 50% (アルファ値としては 0x80) にします。

コマンド 16 - 19 で表示された画像は、グローバルアルファ値と画像データ中のアルファ値の相乗でアルファブレンドが決定されます。

m 22:

アルファブレンドを無効にします。

m 23:

tckgfx.bgr, tckvid1.bgr, tckvid2.bgr を SD カードから読み出して、それぞれ Video1 画面、Video2 画面、Graphics 画面に表示します。

m 24:

transparency color key を有効にします。

コマンド 23 で表示された画像は、コマンド 24 によって影響を受けます。

m 25:

transparency color key を無効にします。

m 26:

fuji32.bgr を SD カードから読み出して、Video1 画面に表示します。

fuji32.bgr は、640 x 480 サイズ、RGB24 (un-packed in 32-bit container) フォーマット (データ並び順は BGRX) の画像データです。

"un-packed in 32-bit container" と言っているのは、BGR 24ビットの後に、適当な pad データを入れて 32 ビットにしているという意味です。

m 27:

fuji32.bgr を SD カードから読み出して、Video1 画面に表示します。

1行 1行の間隔を空けて配置した画像データを表示できるように、DISPC_VID_ROW_INC レジスタへ正しく値設定できているか確かめるためのテストです。

m 28:

fuji32.bgr を SD カードから読み出して、Video1 画面に表示します。

表示する画像は、VRFB Context 1 の 90 度回転画像です。

m 29:

fuji32.bgr を SD カードから読み出して、Video2 画面に表示します。

表示する画像は、VRFB Context 2 の 180 度回転画像です。

m 30:

fuji32.bgr を SD カードから読み出して、Graphics 画面に表示します。

表示する画像は、VRFB Context 3 の 270 度回転画像です。

m 31:

fuji32.bgr を SD カードから読み出して、Video1 画面に表示します。

表示する画像は、VRFB Context 4 の 0 度回転画像です。

m 32:

VRFB に書き込んだデータが、SDRAM 上でどのように配置されるかを確認するためのテストです。

ソースコードのページ に、DSS テストで使用する画像データも一応用意してあります。

dsspic.zip を取得・展開して、すべて SD カードにコピーしてください。

・・・

今までの記事の中で、これらのソースコードが部分的に登場していますが、記事の中のソースコードと現状のソースコードでは、行番号が違っていたりするかもしれません。

ただ、大幅に変わってしまって、原型をとどめていない、というようなことはないと思います。

あと、シリアルコンソールに大量出力すると、シリアルコンソールの表示がたまに乱れるという問題があります。

これは、多分フロー制御をしていないからですね。

ソフトウェアフロー制御をしないといけないなあ・・・と思いつつ、TeraTerm の再起動で誤魔化してしまっています。

最後、蛇足ですが、ソースコードを閲覧するには、GNU GLOBAL が使いやすくてよいと思います。

個人的には、Meadow 上で GLOBAL を使っていますが、非常に快適です。

Google で GNU GLOBAL で引くと、たくさん情報が出てきます。

まだ試したことがないという方、お勧めです。

エッセンスだけ抽出して、できるだけ簡潔に、という記事を目指していたので、ソースコードなんて要らないだろうと思っていたのですが、、、

ひょっとしたら、自分の手元で動かして確かめてみたいという方がおられないとも限らないので、公開することにします。

公開するといっても、x-loader にちょろちょろと手を入れているだけのソースコードですが (^^;

これです↓

ソースコードのページ

ビルド方法については、「開発環境のインストール」「x-loader ビルド」「Windows 開発環境」の回の記事を参照してください。

CodeSourcery をインストールしてあれば、

・tar-ball を展開

・xloader ディレクトリができるので、そこに移動

・make omap3530beagle_config

・make

・./signGP x-load.bin

・cp x-load.bin.ift MLO

・MLO を SD カードにコピー

で OK です。

私がいつも使っている SD カードは、「angstrom ブート」の記事中の方法で作ったもので、FAT32 と ext3 が混在したものなのですが、多分、全体を FAT32 でフォーマットしたものでも大丈夫です。

MLO を、FAT32 領域にコピーしてください。

USER ボタンを押下しながら電源を入れると、beagleboard は SD カードから MLO (=x-loader) をロードして実行します。

PC 側のシリアル端末は、なんでもいいと思いますが、私は TeraTerm を使っています。

ボーレートは、115200 bps にしてください。

無事 x-loader が実行されると、コマンドプロンプトらしき '>' マークが表示されます。

このプロンプトでは、次のコマンドを受け付けます:

i : UART 割り込みテスト

d : UART DMA テスト

t : タイマーテスト

l : LED テスト

b : ボタンテスト

s : SDRAM テスト

n : NAND テスト

sd: SD カードテスト

m : DSS テスト

各テストの内容は、以下です。

UART 割り込みテスト

「UART 割り込みモード」の回に作ったものです。

UART3 を割り込みモードに設定し、'q' が入力されるまでループします。

1 秒おきに "uart_interrupt_test" という文字列をシリアルコンソールに表示します。

'q' 以外を入力すると、"OK" という文字列をシリアルコンソールに表示します。

'q' を入力するとコマンドプロンプトに戻ります。

UART DMA テスト

「UART DMA モード」の回に作ったものです。

UART3 を DMA モードに設定し、シリアルコンソールから 8 文字入力されるまで、ビジーループします。

UART3 に入力された 8 文字は、DMA によって dma_buf 上に転送されます。

転送された 8 文字をシリアルコンソールに出力した後、コマンドプロンプトに戻ります。

タイマーテスト

「タイマーとコンテキストスイッチ」の回に作ったものです。

タスクを 2 つ追加し、3 秒おきにコンテキストスイッチを行います。

'q' を入力するとコマンドプロンプトに戻ります。

ただし、'q' を入力しても、即座にはコマンドプロンプトには戻りません。

メインタスクに実行権が移った時、'q' が入力されたかどうかがチェックされます。

LED テスト

「LED とボタン」の回に作ったものです。

LED を点滅させます。

'q' を入力するとコマンドプロンプトに戻ります。

ボタンテスト

「LED とボタン」の回に作ったものです。

USER ボタンを押下すると、シリアルコンソールに "button pressed", "button released" を表示します。

'q' を入力するとコマンドプロンプトに戻ります。

SDRAM テスト

SDRAM の読み書きを全領域にわたって行います。

テストが完了すると、サイクルカウンターの値をシリアルコンソールに出力してコマンドプロンプトに戻ります。

NAND テスト

「メモリ」の回に作ったものです。

NAND テストは、以下の 4 つのテストから成ります:

ns: NAND ステータステスト

NAND ステータスを取得します。

ステータス取得後、コマンドプロンプトに戻ります。

nr: NAND 読み出しテスト

オフセット 0x07FE0000 から 1 ページ読み出します。

これは、最も高位にあるページです。

読み出し先は、0x88000000 という SDRAM 上の適当なアドレスです。

読み出し完了後、読み出した値を表示して、コマンドプロンプトに戻ります。

ne: NAND 消去テスト

オフセット 0x07FE0000 からの 1 ページを消去します。

消去完了後、コマンドプロンプトに戻ります。

np: NAND プログラムテスト

2 つの引数、off と len を取ります(引き数 off は 1 桁の値のみ・・・)。

np 6 10 のように入力して引数を渡します。

オフセット 0x07FE0000 + off に 0x88000000 に書かれているデータを長さ len 分だけ書き込みます。

書き込み完了後、コマンドプロンプトに戻ります。

SD カードテスト

「FAT ファイルシステム」の回に作ったものです。

1 つの引き数 blknr を取ります。

sd 10 のように入力して引数を渡します。

SD カードから、ブロック番号 blknr から 1 ブロック分読み出します。

読み出した値をシリアルコンソールに出力した後、コマンドプロンプトに戻ります。

DSS テスト

「LCD 表示」「LCD 表示 (2)」の回に作ったものです。

このテストを試すには、HDMI-DVI 変換ケーブルで beagleboard と液晶ディスプレイを接続しておく必要があります。

DSS テストは、32 個のサブコマンドがあります。

'm' の後に、空白文字を 1 つ挟んで、サブコマンド番号を入力します。

m 0:

640 x 480 @ 60Hz で DSS を初期化します。

m 1:

640 x 480 @ 75Hz で DSS を初期化します。

m 2:

800 x 600 @ 60Hz で DSS を初期化します。

m 3:

1024 x 768 @ 60Hz で DSS を初期化します。

m 4:

1280 x 1024 @ 60Hz で DSS を初期化します。

m 5:

fuji.bgr を SD カードから読み出して、Video1 画面に表示します。

fuji.bgr は、640 x 512 サイズ、RGB24 フォーマット (データ並び順は BGR) の画像データです。

m 6:

Video1 画面を無効化します。

m 7:

Video2 画面を無効化します。

m 8:

Graphics 画面を無効化します。

m 9:

asa.bgr, cake.bgr, shin.bgr を SD カードから読み出して、それぞれ Video1 画面、Video2 画面、Graphics 画面に表示します。

asa.bgr, cake.bgr, shin.bgr は、いずれも 640 x 512 サイズ、RGB24 フォーマット (データ並び順は BGR) の画像データです。

画像の配置は、1280 x 1024 にちょうど収まるような配置にしています。

m 10:

asa.bgr, cake.bgr, shin.bgr を SD カードから読み出して、それぞれ Video1 画面、Video2 画面、Graphics 画面に表示します。

コマンド 9 と違って、重なり表示をするようにしています。

ついでに重なったまま動きます。

m 11:

fuji.bgr を SD カードから読み出して、Video1 画面に拡大表示します。

m 12:

fuji.bgr を SD カードから読み出して、Video1 画面に縮小表示します。

※ 1280 x 1024 でこれを実行すると、画面が乱れてしまいますので、1024 x 768 でお試しください。

m 13:

fuji.bgr を SD カードから読み出して、Video1 画面上で徐々に拡大させていきます。

m 14:

asa_a.bgr, cake_a.bgr, shin_a.bgr を SD カードから読み出して、それぞれ Video1 画面、Video2 画面、Graphics 画面に表示します。

asa_a.bgr, cake_a.bgr, shin_a.bgr は、いずれも 640 x 512 サイズ、ARGB32 フォーマット (データ並び順は BGRA) の画像データです。

アルファブレンドは、すべてのピクセルにおいて、50% (アルファ値としては 0x80) にしています。

画像の配置は、1280 x 1024 にちょうど収まるような配置にしています。

m 15:

asa_a.bgr, cake_a.bgr, shin_a.bgr を SD カードから読み出して、それぞれ Video1 画面、Video2 画面、Graphics 画面に表示します。

コマンド 14 と違って、重なり表示をするようにしています。

※ 1280 x 1024 でこれを実行すると、画面が乱れてしまいますので、1024 x 768 でお試しください。

m 16:

asa.bgr を SD カードから読み出して、Video2 画面に表示します。

m 17:

asa_a.bgr を SD カードから読み出して、Video2 画面に表示します。

m 18:

asa_a0.bgr を SD カードから読み出して、Video2 画面に表示します。

asa_a0.bgr は 640 x 512 サイズ、ARGB32 フォーマットの画像データ (データ並び順は BGRA) で、アルファブレンドはすべてのピクセルにおいて、100% (アルファ値としては 0x00)にしています。

アルファブレンドを有効にすると、asa_a0.bgr は透過率 100% となって表示されません。

m 19:

asa_aff.bgr を SD カードから読み出して、Video2 画面に表示します。

asa_aff.bgr は 640 x 512 サイズ、ARGB32 フォーマットの画像データ (データ並び順は BGRA) で、アルファブレンドはすべてのピクセルにおいて、0% (アルファ値としては 0xff)にしています。

m 20:

アルファブレンドを有効にし、Video2 画面、Graphics 画面のグローバルアルファブレンドを 0% (アルファ値としては 0xff) にします。

アルファブレンド 0% は、全く透過させないことを意味します。

コマンド 16 - 19 によって表示された画像は、画像データ中のアルファ値によってのみアルファブレンドが決定されます。

m 21:

アルファブレンドを有効にし、Video2 画面、Graphics 画面のグローバルアルファブレンドを 50% (アルファ値としては 0x80) にします。

コマンド 16 - 19 で表示された画像は、グローバルアルファ値と画像データ中のアルファ値の相乗でアルファブレンドが決定されます。

m 22:

アルファブレンドを無効にします。

m 23:

tckgfx.bgr, tckvid1.bgr, tckvid2.bgr を SD カードから読み出して、それぞれ Video1 画面、Video2 画面、Graphics 画面に表示します。

m 24:

transparency color key を有効にします。

コマンド 23 で表示された画像は、コマンド 24 によって影響を受けます。

m 25:

transparency color key を無効にします。

m 26:

fuji32.bgr を SD カードから読み出して、Video1 画面に表示します。

fuji32.bgr は、640 x 480 サイズ、RGB24 (un-packed in 32-bit container) フォーマット (データ並び順は BGRX) の画像データです。

"un-packed in 32-bit container" と言っているのは、BGR 24ビットの後に、適当な pad データを入れて 32 ビットにしているという意味です。

m 27:

fuji32.bgr を SD カードから読み出して、Video1 画面に表示します。

1行 1行の間隔を空けて配置した画像データを表示できるように、DISPC_VID_ROW_INC レジスタへ正しく値設定できているか確かめるためのテストです。

m 28:

fuji32.bgr を SD カードから読み出して、Video1 画面に表示します。

表示する画像は、VRFB Context 1 の 90 度回転画像です。

m 29:

fuji32.bgr を SD カードから読み出して、Video2 画面に表示します。

表示する画像は、VRFB Context 2 の 180 度回転画像です。

m 30:

fuji32.bgr を SD カードから読み出して、Graphics 画面に表示します。

表示する画像は、VRFB Context 3 の 270 度回転画像です。

m 31:

fuji32.bgr を SD カードから読み出して、Video1 画面に表示します。

表示する画像は、VRFB Context 4 の 0 度回転画像です。

m 32:

VRFB に書き込んだデータが、SDRAM 上でどのように配置されるかを確認するためのテストです。

ソースコードのページ に、DSS テストで使用する画像データも一応用意してあります。

dsspic.zip を取得・展開して、すべて SD カードにコピーしてください。

・・・

今までの記事の中で、これらのソースコードが部分的に登場していますが、記事の中のソースコードと現状のソースコードでは、行番号が違っていたりするかもしれません。

ただ、大幅に変わってしまって、原型をとどめていない、というようなことはないと思います。

あと、シリアルコンソールに大量出力すると、シリアルコンソールの表示がたまに乱れるという問題があります。

これは、多分フロー制御をしていないからですね。

ソフトウェアフロー制御をしないといけないなあ・・・と思いつつ、TeraTerm の再起動で誤魔化してしまっています。

最後、蛇足ですが、ソースコードを閲覧するには、GNU GLOBAL が使いやすくてよいと思います。

個人的には、Meadow 上で GLOBAL を使っていますが、非常に快適です。

Google で GNU GLOBAL で引くと、たくさん情報が出てきます。

まだ試したことがないという方、お勧めです。

beagleboard を触ろう - LCD 表示 (2) [組み込みソフト]

前回記事で、外部 LCD に画像を表示させてみましたが、今回はその続きです。

LCD に画像を表示するには、Display Subsystem (DSS) モジュールを使えばいいのでした。

DSS は、Video1, Video2, Graphics 各画面を独立に表示できます。

DSS を設定して、Video1, Video2, Graphics 画面に画像を表示させたというところまでが、前回やったことです。

今回は、アルファブレンド、Transparent Color Key、拡大・縮小、回転を試してみます。

アルファブレンド

アルファブレンドは、画像を透過させる機能です。

アルファ値の大小によって、透過度が変わってきます。

アルファ値は 0x00 - 0xff まで指定できて、0x00 は 100 % を表し、0xff は 0% を表します。

アルファブレンド 100% は、100% 透過することを意味し、0% は全く透過しないことを意味します。

こんなオリジナル↓に対して、

50% 透過だと、こんな感じ↓です。

背景画面の緑色が透けて見えます。

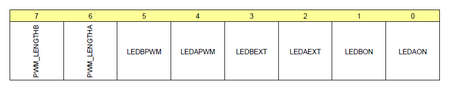

アルファブレンドを有効にするかどうかを決定するのは、DISPC_CONFIG レジスタの LCDALPHABLENDERENABLE ビットです。

アルファブレンドが適用されるのは、Video2 画面、および Graphics 画面です。

Video1 画面には適用されません。

アルファ値は、DISPC_GLOBAL_ALPHA レジスタに設定する値か、もしくは画像データに埋め込んだ値で決定することができます。

DISPC_GLOBAL_ALPHA レジスタでアルファ値を設定した場合は、Video2 画面, Graphics 画面の全ピクセルにおいて、設定したアルファ値が一律に適用されます。

一方、画像データに埋め込む場合は、各ピクセル毎にアルファ値を設定・適用できます。

DSS がサポートしている画像フォーマットに、ARGB 16, ARGB 32, RGBA 32 というのがありますが、この A がアルファ値を表します。

DISPC_GLOBAL_ALPHA レジスタでアルファ値を設定した場合、Video2 画面、Graphics 画面の画像フォーマットが ARGB/RGBA か、それ以外の (A なし) フォーマットかに関わらず、画面は透過します。

ARGB/RGBA であれば、相乗でさらに透過します。

DISPC_GLOBAL_ALPHA レジスタのアルファブレンドが 50%、画像フォーマットが RGB 32 の場合は、こうなります↓

DISPC_GLOBAL_ALPHA レジスタのアルファブレンドが 50%、画像フォーマットが RGBA 32 で、各ピクセルのアルファブレンドが 50% の場合は、こうなります↓

透過度が大きくなるので、緑っぽさが強くなりますね。

DISPC_GLOBAL_ALPHA レジスタのアルファブレンドが 0%、画像フォーマットが RGBA 32 で、各ピクセルのアルファブレンドが 0% の場合は、透過しません↓

なお、アルファブレンドを有効にした場合、Video1, Video2, Graphics 画面の表示優先順位が変わります。

アルファブレンドが無効の場合は、表示優先順位は、Video2 > Video1 > Graphics > 背景画面 です↓(前回記事にて既出)

アルファブレンドが有効の場合は、これが Graphics > Video2 > Video1 > 背景画面 となります↓

実際にアルファブレンドを有効にして重ね合わせてみると、こんな感じです↓

この写真では、優先順位がどうだか、わけが分かりませんが (^^;

上の写真は、1024 x 768 @ 60Hz で試したものです。

これを、1280 x 1024 @ 60Hz で試すと、こんな風になります↓

うむむ、なんか、乱れてて変です。

うーん・・・と悩ましく思っていると、1280 x 1024 @ 60Hz の時は、ピクセルクロック 108MHz という、無理目な値で動作させていることが思い出されてきました。

OMAP35x TRM には、"Programmable pixel rate up to 75MHz" という記述があって、108MHz は上限オーバーではないかと思っていたのです。

そのせいかどうか、定かではありませんが・・・。

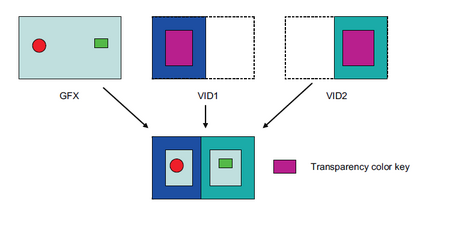

Transparent Color Key

Video1 画面、Video2 画面、Graphics 画面が重なって表示される場合、重なり部分は、表示優先順位に従って表示されます。

アルファブレンドなしの場合は、再掲で恐縮ですが、表示優先度は Video2 > Video1 > Graphics > 背景画面 です。

Video1/Video2 画面と Graphics 画面が重なると、Graphics 画面の重なった部分は表示されません。

Transparent Color Key は、指定した箇所を透明にして、下の画面を見せるようにする機能です。

透明にする箇所は、色によって指定します。

この機能は、絵で見れば一目瞭然です。

設定は簡単です。

DISPC_CONFIG レジスタの TCKLCDSELECTION ビットと TCKLCDENABLE ビットを立て、DISPC_TRANS_COLOR_0 レジスタに、透明にする箇所の色を設定するだけです。

実際にやってみましょう。

Video1, Video2, Graphics 画面は、それぞれ↓のようなものです。

Video1

Video2

Graphics

Transparency Color Key を無効のままにして Video1, Video2, Graphics 画面を重ねると、↓のようになります。

Graphics 画面は完全に隠れます。

ここで、Transparency Color Key を有効にして、紫色を Transparency Color Key として設定すると、↓のようになります。

紫だった部分が、透けて見えるようになることが分かりますね。

拡大・縮小

Video1, Video2 画面は、拡大・縮小表示させる機能を持っています。

Graphics 画面は、拡大・縮小できません。

拡大・縮小に関して、詳しいことは全然知らないのですが (^^; 元の画素の近傍何点かを使って、拡大・縮小した画素を作るものと思います。

DSS の拡大・縮小機能は、水平方向 5 点、垂直方向 3 点を使うか、もしくは水平方向 5 点、垂直方向 5 点を使うか、いずれかが選択できます。

これら近傍点の画素に重み付け係数をかけ合わせ、新しい画素を作るようになっていると思います。

レジスタ設定的にも、重み付け係数をいちいち設定してやる必要があります。

拡大・縮小のアルゴリズムによって、重み付け係数は適当に設定してね、ということだと思いますが、素人にはどうすればいいか、さっぱり分かりません (T_T)

OMAP35x TRM には、Max-Fauque-Berthier method を使う場合の重み付け係数の値が載っていました。

Max-Fauque-Berthier method とは??

・・・うーん、さっぱり分かりません。

さっぱり分かりませんが、Max-Fauque-Berthier method による拡大・縮小表示を試します。

設定するレジスタは、前回の↓に加えて、

DISPC_VIDn_BA0

DISPC_VIDn_POSITION

DISPC_VIDn_SIZE

DISPC_VIDn_PICTURE_SIZE

DISPC_VIDn_FIFO_THRESHOLD

DISPC_VIDn_FIFO_SIZE_STATUS

DISPC_VIDn_ROW_INC

DISPC_VIDn_PIXEL_INC

DISPC_VIDn_ATTRIBUTES

以下を追加で設定します↓

DISPC_VIDn_FIR

DISPC_VIDn_ACCU

DISPC_VIDn_FIR_COEF_Hi

DISPC_VIDn_FIR_COEF_HVi

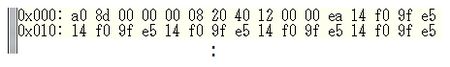

275: /* VINC, HINC */

276: firvinc = 1024 * (orgsizey - 1) / (sizey - 1);

277: firhinc = 1024 * (orgsizex - 1) / (sizex - 1);

278: __raw_writel((firvinc << 16) | firhinc, DISPC_VID_FIR(n));

DISPC_VIDn_FIR レジスタの VIDFIRVINC, VIDFIRHINC に、垂直方向の拡大・縮小率、水平方向の拡大・縮小率を設定します。

設定する値は、1024 * (元の長さ - 1) / (拡大・縮小後の長さ - 1) です。

280: /* accumulator */

281: __raw_writel(0x0, DISPC_VID_ACCU(n, 0));

このレジスタはよく分からないのですが、LCD の場合は 0 にせよと OMAP35x TRM に書いてあったので、盲目的に 0 を設定します (^^;

283: /* coefficients */

284: __raw_writel(0x00800000, DISPC_VID_FIR_COEF_H(n, 0));

285: __raw_writel(0x00800000, DISPC_VID_FIR_COEF_HV(n, 0));

286: __raw_writel(0x0D7CF800, DISPC_VID_FIR_COEF_H(n, 1));

287: __raw_writel(0x037B02FF, DISPC_VID_FIR_COEF_HV(n, 1));

288: __raw_writel(0x1E70F5FF, DISPC_VID_FIR_COEF_H(n, 2));

289: __raw_writel(0x0C6F05FE, DISPC_VID_FIR_COEF_HV(n, 2));

290: __raw_writel(0x335FF5FE, DISPC_VID_FIR_COEF_H(n, 3));

291: __raw_writel(0x205907FB, DISPC_VID_FIR_COEF_HV(n, 3));

292: __raw_writel(0xF74949F7, DISPC_VID_FIR_COEF_H(n, 4));

293: __raw_writel(0x00404000, DISPC_VID_FIR_COEF_HV(n, 4));

294: __raw_writel(0xF55F33FB, DISPC_VID_FIR_COEF_H(n, 5));

295: __raw_writel(0x075920FE, DISPC_VID_FIR_COEF_HV(n, 5));

296: __raw_writel(0xF5701EFE, DISPC_VID_FIR_COEF_H(n, 6));

297: __raw_writel(0x056F0CFF, DISPC_VID_FIR_COEF_HV(n, 6));

298: __raw_writel(0xF87C0DFF, DISPC_VID_FIR_COEF_H(n, 7));

299: __raw_writel(0x027B0300, DISPC_VID_FIR_COEF_HV(n, 7));

これらが、近傍点の重み付け係数です。

Max-Fauque-Berthier method に従って、値を設定します。(キリッ

(設定する値は、OMAP35x TRM に載っています。)

DISPC_VIDn_BA0

DISPC_VIDn_POSITION

DISPC_VIDn_SIZE

DISPC_VIDn_PICTURE_SIZE

DISPC_VIDn_FIFO_THRESHOLD

DISPC_VIDn_FIFO_SIZE_STATUS

DISPC_VIDn_ROW_INC

DISPC_VIDn_PIXEL_INC

DISPC_VIDn_ATTRIBUTES

これらのレジスタ↑は、前回と同じように設定します。

前回と違うところは、

- DISPC_VIDn_SIZE レジスタに拡大・縮小後の表示サイズを、DISPC_VIDn_PICTURE_SIZE レジスタに元の大きさを設定すること

- DISPC_VIDn_ATTRIBUTES レジスタの VIDRESIZEENABLE ビットフィールドを設定して拡大・縮小を有効化すること

です。

DISPC_VIDn_ATTRIBUTES レジスタの VIDRESIZEENABLE ビットフィールドには、

- 拡大・縮小しない場合は 0

- 水平方向に拡大・縮小する場合は 1

- 垂直方向に拡大・縮小する場合は 2

- 水平方向・垂直方向ともに拡大・縮小する場合は 3

を設定します。

実際にやってみると、こんな感じです↓

元画像

1.5 倍に拡大

5/8 に縮小

10msec 毎に 1 ピクセルずつ拡大してみました↓

ダウンロードは🎥こちら

回転

90度、180度、270度、回転させた画像を表示させることができます。

回転表示させるには、方法が 2 つあります。

1 つは、DSS の DMA engine の回転機能を使う方法と、SDRAM コントローラの回転機能を使う方法です。

(内臓 SRAM に画像データを置く場合は、前者の方法しか使えません。)

OMAP35x TRM には、パフォーマンスの観点から後者をお勧めします、というようなことが書いてあります。

なので、ここでも素直に後者の方法で回転を試してみます。

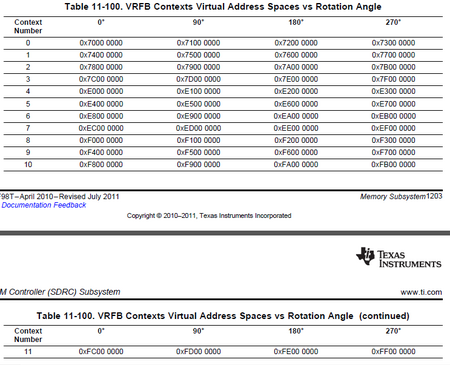

OMAP3530 内の SDRAM Controller Subsystem は、SDRC と SMS というモジュールから成っています。

(SDRC については、「メモリ」の回で触れました。)

SMS は、メモリアクセス要求のスケジューリングをしたり、アクセス制限をつけたりする機能を持つモジュールですが、Rotation engine も持っています。

Rotation engine は、OMAP35x TRM では、VRFB とか、Rotation engine とか、略して RE とか呼ばれています。

ある特定のアドレスでアクセスすると、Rotation engine を経由して SDRAM にアクセスするようになっています。

この特定のアドレスは、0x7000_0000 - 0x7FFF_FFFF までの 256MB の領域と、0xE000_0000 - 0xFF00_0000 までの 512MB の領域として割り当てられています。

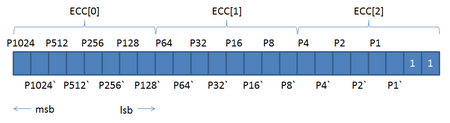

下の表のように、この領域は 12 分割されています。

これらは、12個の独立した領域です。

どのように使うかというと、

例えば、ある画像 A を、0x7000_0000 に書き込んだとします。

0x7000_0000 から読み出すと、画像 A の 0 度回転した画像データが得られます。

0x7100_0000 から読み出すと、画像 A の 90 度回転した画像データが得られます。

0x7200_0000 から読み出すと、画像 A の 180 度回転した画像データが得られます。

0x7300_0000 から読み出すと、画像 A の 270 度回転した画像データが得られます。

また、他の画像 B を、0x7400_0000 に書き込んだとします。

0x7400_0000 から読み出すと、画像 B の 0 度回転した画像データが得られます。

0x7500_0000 から読み出すと、画像 B の 90 度回転した画像データが得られます。

0x7600_0000 から読み出すと、画像 B の 180 度回転した画像データが得られます。

0x7700_0000 から読み出すと、画像 B の 270 度回転した画像データが得られます。

こんな感じで、12 分割された各領域を使うことができます。

この各領域のことを、OMAP35x TRM では、VRFB Context と呼んでいます。

Texas Instruments としては、携帯端末を横向き、縦向きに変えた際に画像を回転させる時とかに、この機能を使いなさいよ、ということみたいです。

各 VRFB Context の実体は、SMS_ROT_PHYSICALn レジスタによって設定します。

例えば、VRFB Context 1 の実体を 0x8000_0000 (= SDRAM 先頭アドレス) に設定するには、SMS_ROT_PHYSICAL1 レジスタに 0x8000_0000 を設定します。

こうしておけば、VRFB Context1 の 0 度回転領域 0x7400_0000 に書き込んだ画像データは、 実アドレス 0x8000_0000 の領域に書き込まれます。

また、90 度回転領域 0x7500_0000 から読み出されるデータは、実アドレス 0x8000_0000 の領域から読み出されます。

もちろん、180 度回転領域 0x7600_0000, 270 度回転領域 0x7700_0000 から読み出されるデータも、実アドレス 0x8000_0000 の領域から読み出されたものになります。

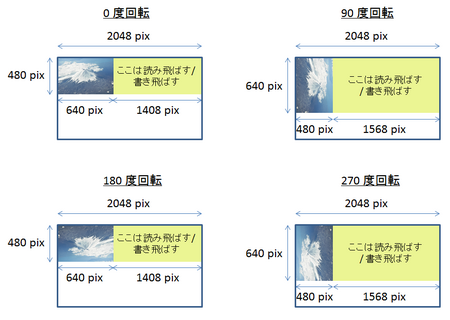

各回転領域における画像データの配置は、以下のようになります。

どの回転領域からアクセスする場合でも、横幅 2048 ピクセルの領域内に画像データが配置されているものとしてアクセスする必要があります。

例えば、0x7400_0000 (VRFB Context 1 の 0 度回転領域) にサイズ 640 x 480、画像フォーマット RGB32 (1 ピクセル = 4 バイト) の画像データを書き込むことを考えてみましょう。

まず、先頭の 1 行分 640 ピクセル (= 640 x 4 バイト) を、0x7400_0000 に書き込みます。

(0x7400_0000 - 0x7400_0A00)

次の 2 行目は、0x7400_0000 + 2048 x 4 = 0x7400_2000 から書き込みます。

(0x7400_2000 - 0x7400_2A00)

同様に、次の 3 行目は、0x7400_2000 + 2048 x 4 = 0x7400_4000 から書き込みます。

(0x7400_4000 - 0x7400_4A00)

以下、同様です。

このように、行と行の間には、適切にオフセットを入れる必要があります。

上の例だと、オフセットの値は、(2048 - 640) x 4 になります。

0x7500_0000 (VRFB Context 1 の 90 度回転領域) から、画像データを読んでみましょう。

90 度回転なので、480 x 640 の画像になります。

まず、先頭の 1 行分 480 ピクセル (= 480 x 4 バイト) を、0x7500_0000 から読み出します。

(0x7500_0000 - 0x7500_0780)

次の 2 行目は、0x7500_0000 + 2048 x 4 = 0x7500_2000 から読み出します。

(0x7500_2000 - 0x7500_2780)

同様に、次の 3 行目は、0x7500_2000 + 2048 x 4 = 0x7500_4000 から読み出します。

(0x7500_4000 - 0x7500_4780)

以下、同様です。

VRFB にアクセスするには、このようなルールを守ってアクセスする必要があります。

さもないと、正しい回転画像が得られません。

DSS に VRFB から読み出させる場合は、DSS の DMA engine が適切にオフセットを挟むように、設定する必要があります。

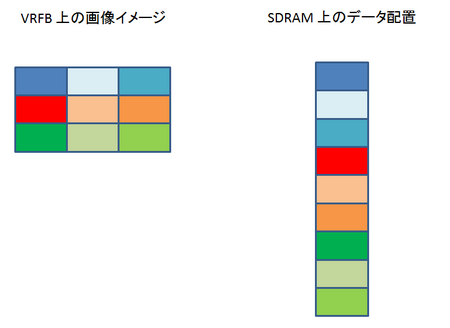

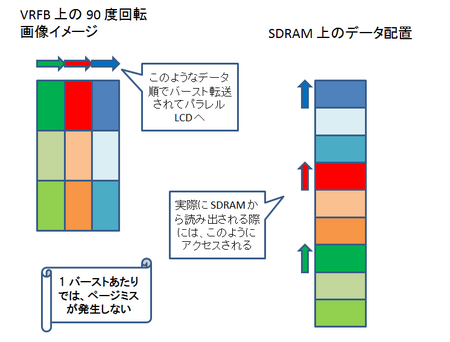

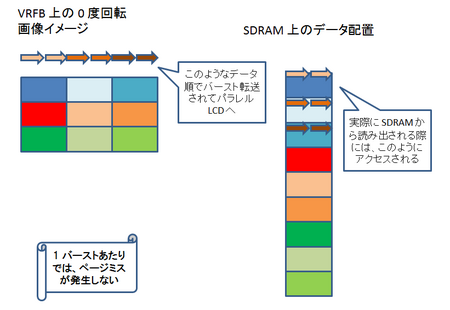

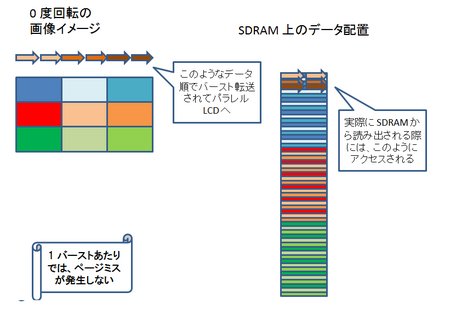

0x7400_0000 (VRFB) に書き込まれたデータは、0x8000_0000 (SDRAM) ではどのように配置されるのでしょうか。

多分ですが、こんなです↓

VRFB を介さないで、普通に画像データを書き込んだ場合は、以下のようになります↓

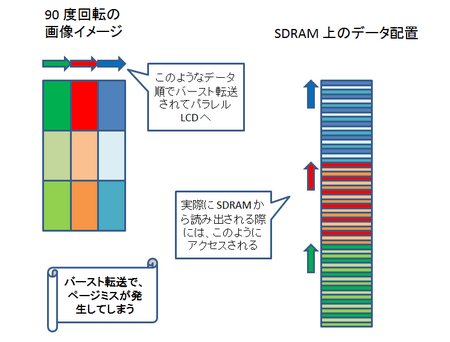

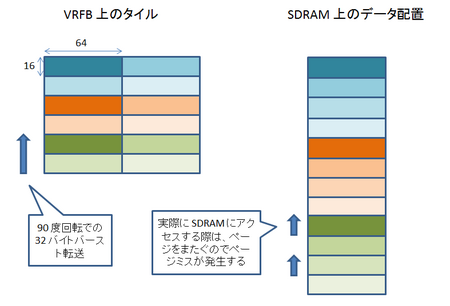

VRFB を介さないで書き込んだ場合、90 度回転させるケースを考えると、DSS の DMA engine が SDRAM からパラレル LCD 出力にデータを転送する際、各バースト転送ごとにページミスが発生してしまいます。

しかし、VRFB 経由で書き込まれたデータの方は、ページミスが発生しません。

VRFB を介さないで書き込んだ場合、0 度回転、180 度回転の場合はページミスが発生しません。

VRFB 経由で書き込まれたデータの方も、0 度回転、180 度回転の場合でもページミスが発生しません。

VRFB を介さないで書き込んだ場合は、90 度回転、270 度回転の場合にページミスが発生してしまいますが、VRFB 経由の場合は、どの回転角度でもページミスが発生しません。

というわけで、VRFB を使うと、DSS の DMA engine の回転機能を使う場合に比べて、パフォーマンスが向上します。(するはずです。)

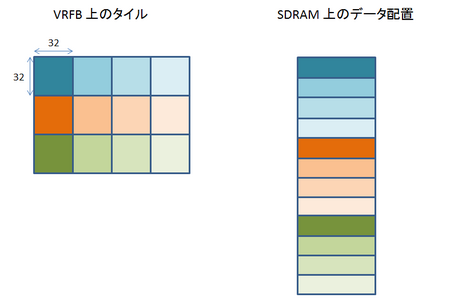

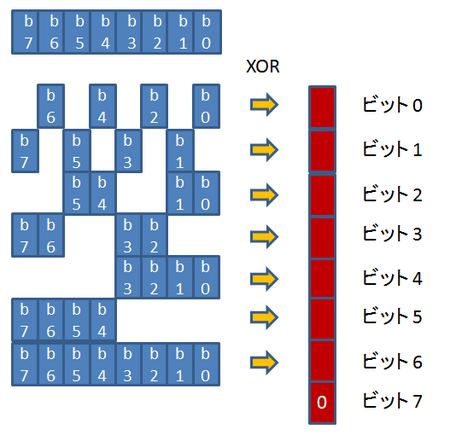

SMS Rotation engine (VRFB) は、タイルベースで画像データを扱います。

実際にプログラミングする際には、タイルサイズを定義する必要があります。

タイルサイズの定義は、VRFB に書き込んだデータが、実際の SDRAM にどのように配置されるかに効いてきます。

タイルサイズは、SDRAM のページサイズと一致させておく必要があります。

beagleboard に搭載されている SDRAM のページサイズは、1024 バイトです。(多分。)

1024 バイトのタイルサイズだと、考えられるのは、

- 32 x 32

- 64 x 16 (16 x 64)

- 128 x 8 (8 x 128)

- 256 x 4 (4 x 256)

- 512 x 2 (2 x 512)

- 1024 x 1 (1 x 1024)

があります。

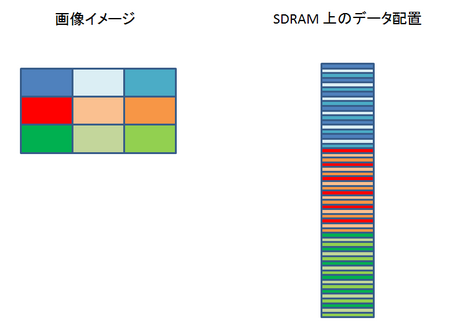

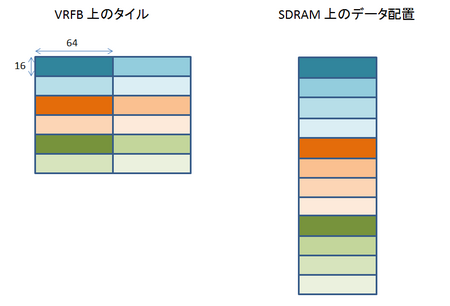

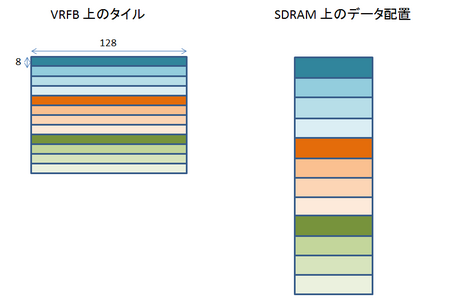

このうち、32 x 32, 64 x 16, 128 x 8 の場合の、VRFB と実 SDRAM の対応関係を見てみましょう。

このように、タイルサイズの違いによって、SDRAM に格納されるデータの配置が変わります。

では、どのタイルサイズを選択すればいいかというと、できるだけ正方形に近い組み合わせです。

タイルサイズ (= SDRAM のページサイズ) が 1024 バイトならば、32 x 32 にしておけば OK です。

64 x 16 でも、そんなには悪くありません。

しかし、64 x 16 の場合、DSS の DMA engine のバースト長を 32 バイトにしている時は、バースト転送するたびに SDRAM でページミスが発生することになってしまいます。

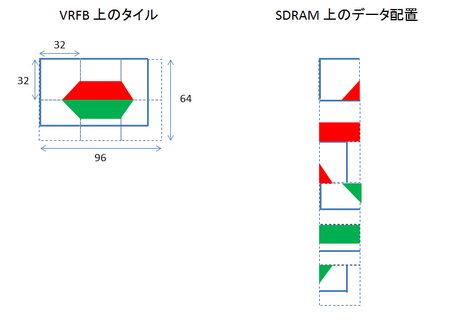

実際の画像は、このタイル上に配置するようなイメージです。

VRFB の設定レジスタ SMS_ROT_SIZEn にイメージ幅、イメージ高さを指定する必要があるのですが、設定する値は、実際の画像の大きさではなく、タイルの大きさです。

下の絵で言えば、イメージ幅は 96, イメージ高さは 64 を指定します。

タイル 1 つが、SDRAM の 1 ページ分に相当し、適切に並び替えられて SDRAM に配置されます。

画像がタイルサイズにぴったり合うと、ちょっとだけですが、扱いやすくなります。

今回は、640 x 480 の画像を使います。

これだと、32 x 32 の大きさのタイルが 20 x 15 になって、幅、高さとも整数倍になります。

それでは、実際に回転させてみましょう。

設定するレジスタは、SMS Rotation engine 関連では、以下の 3 つです。

SMS_ROT_CONTROLn

SMS_ROT_SIZEn

SMS_ROT_PHYSICAL_BAn

(n = 0 - 11)

VRFB Context は 12 個あるので、上記レジスタも 12 セットあります。

これらのレジスタには、タイルサイズ、ピクセルサイズ、イメージ幅、イメージ高さ、画像を配置する SDRAM 上の実アドレスを指定します。

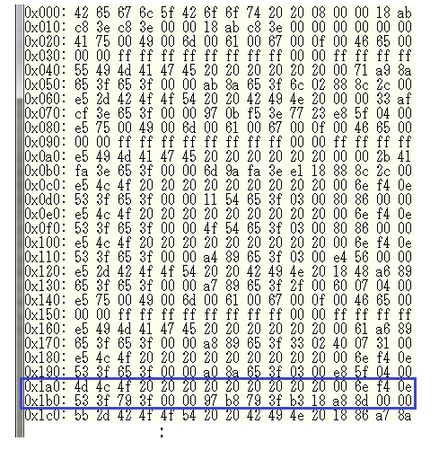

461: int set_vrfb(int n, unsigned long ba, int orgsizex, int orgsizey, int format)

462: {

463: unsigned char ph, pw, ps;

464: unsigned short imagewidth, imageheight;

465: unsigned char bpp;

466:

467: /* configure page width and height as 32x32, considering page size is 1KB */

468: pw = 5;

469: ph = 5;

470:

471: switch (format) {

472: case BITMAP8:

473: ps = 0;

474: bpp = 1;

475: break;

476: case RGB12_16:

477: case ARGB16:

478: case RGB16:

479: ps = 1;

480: bpp = 2;

481: break;

482: case RGB24_32:

483: case ARGB32:

484: case RGBA32:

485: ps = 2;

486: bpp = 4;

487: break;

488: default:

489: return -1;

490: }

491:

492: if (orgsizex * bpp % 32)

493: imagewidth = (orgsizex / 32 + 1) * 32;

494: else

495: imagewidth = orgsizex;

496: if (orgsizey % 32)

497: imageheight = (orgsizey / 32 + 1) * 32;

498: else

499: imageheight = orgsizey;

500:

501: __raw_writel((ph << 8) | (pw << 4) | ps, SMS_ROT_CONTROL(n));

502: __raw_writel((imageheight << 16) | imagewidth, SMS_ROT_SIZE(n));

503: __raw_writel(ba, SMS_ROT_PHYSICAL_BA(n));

468 行目、469 行目で、タイルサイズを決定しています。

32x32 のタイルサイズにするには、レジスタに設定する値は 32 ではなく、2 のべき乗数に当たる 5 になります。

471 行目から 487 行目で、引数で与えられた画像フォーマット値に対して、ピクセルサイズ ps を得ています。

ピクセルサイズ ps も、バイト数そのものではなく、2 のべき乗数を指定します。

492 行目から 499 行目で、イメージ幅、イメージ高さを決定しています。

画像幅、画像高さが、タイル幅、タイル高さの整数倍ならば、イメージ幅、イメージ高さは画像幅、画像高さと一致します。

501 行目から、503 行目で SMS Rotation engine 関連のレジスタに値を設定します。

n は、0 - 11 の間の値です。

SMS Rotation engine の設定はこれだけです。

意外と簡単です。

後は、画像を VRFB に書き込んで、別角度の VRFB から読み出すだけです。

VRFB 0 度回転の領域に画像データを書き込んで、0 度回転、90 度回転、180 度回転、270 度回転の領域を DSS に読み取らせてみましょう。

先述のように、DSS に正しく読み取らせるには、行読み出しごとに適切なオフセットを加えないといけないことに注意です。

これは、DISPC_VID_ROW_INC(n) レジスタに "オフセット値 + 1" を設定することにより、実現します。

もちろん、0 度回転の領域に画像データを書き込む際にも、適切にオフセットを挟みます。

という感じで、正しく動作しました。

ところが、、、

Video1 画面に 90 度回転画像を、Video2 画面に 180 度回転画像を、Graphics 画面に 270 度回転画像を同時に表示させると、なんかおかしくなってしまいました。

うーん・・・。

これはちょっと謎です (T_T)

・・・

今回、DSS の応用機能 (?) を触ってみました。

グラフィック関連で言えば、beagleboard 上で使えるデバイスとしては、Imagination Technologies 社の 2D/3D アクセラレータ POWERVR SGX530 があります。

こちらは、どうやら仕様は非公開のようです。

Linux のドライバは、バイナリのみ提供されているようですが。

というわけで、こちらは触りません (^^;

beagleboard を触ろう - LCD 表示 [組み込みソフト]

beagleboard から、DVI ケーブル経由で液晶ディスプレイ (LCD) に画像を表示させてみましょう。

beagleboard と液晶ディスプレイは、HDMI-DVI 変換ケーブルを使って接続します。

ちなみに、自分の LCD は、DVI コネクタと一緒にアナログ RGB コネクタも持つ、かなり古いものです。

beagleboard に搭載されている HDMI コネクタは、形こそ HDMI ですが、機能的には DVI だそうで、DVI コネクタはでかいので、代わりに小さな HDMI コネクタを載せているそうです。

本来 HDMI は、画像データの他に音声データも運ぶことができますが、beagleboard の場合は、画像データのみ運べます。

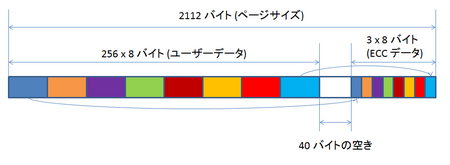

beagleboard から画像データを送り出すのは、Display Subsystem (DSS) というモジュールです。

DSS を制御することにより、液晶ディスプレイに画像を表示させることができます。

DSS は、様々な外部出力に対応しています。

1. パラレル LCD 出力

2. Remote Frame Buffer Interface (RFBI)

3. Serial Display Interface (SDI)

4. Display Serial Interface (DSI)

5. NTSC/PAL

DVI ケーブルでの LCD 表示は、1 のパラレル LCD 出力を使います。

2 は、MIPI DBI プロトコルというものを使うみたいです。

MIPI は、Mobile Industry Processor Interface の略で、MIPI Alliance によって策定された規格 (インターフェース仕様/プロトコル) と思います。

DBI は、ディスプレイにパラレル出力する規格です、多分。

3 は、TI (Texas Instruments) ユニークな規格かも。

TI Flatlink なるもののようです。

4 は、2 と同じく MIPI の規格です。

こちらは、2 と違ってシリアル出力です。

5 は、TV ですね。

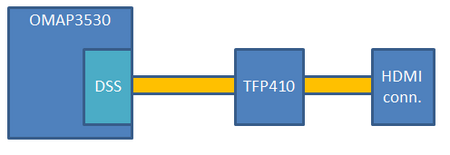

beagleboard では、パラレル LCD 出力の先には、TFP410 というチップがあり (SRM では DVI-D framer chip と呼ばれている)、これがパラレル LCD 出力を DVI-D 信号に変換してくれます。

DSS を適切に設定して、パラレル LCD 出力から画像データを流すようにすることが、今回の目的です。

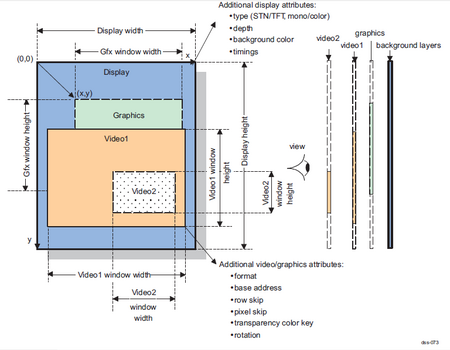

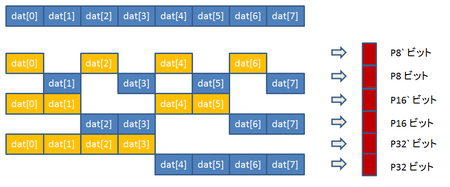

DSS の表示機能をさらっと見てみましょう。

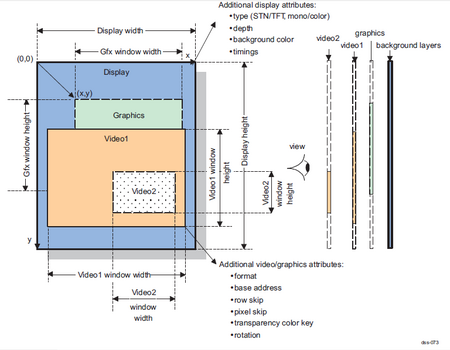

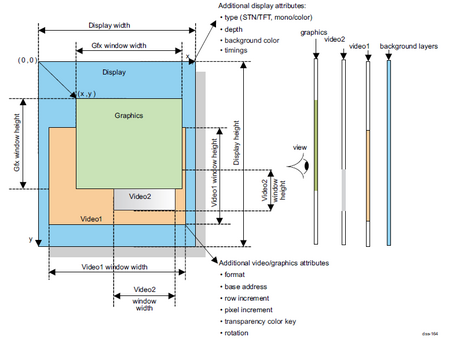

DSS が表示する画面は、下図のように、背景画面、Video1 画面、Video2 画面、Graphics 画面から成ります。

Video1 画面、Video2 画面、Graphics 画面は、それぞれ有効・無効を設定できます。

表示優先順位は、Video2 > Video1 > Graphics > 背景画面となります。

Video1, Video2, Graphics の大きさは、背景画面に収まる範囲内で、自由に設定することができます。

表示データは、それぞれ指定されたメモリアドレスから供給されます。

各々に専用の領域を割り当ててやれば、独立した画面を表示することができます。

背景画面の大きさは、LCD に合わせて設定します。

800x600 とか、1024x768 とか、LCD がサポートしているサイズを設定します。

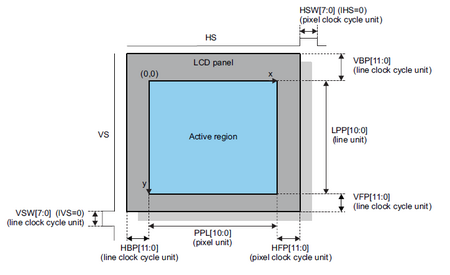

画面サイズを設定するとともに、タイミングパラメータの設定も必要です。

設定するタイミングパラメータは、水平フロントポーチ、水平同期パルス幅、水平バックポーチ、垂直フロントポーチ、垂直同期パルス幅、垂直バックポーチです。

これらは、LCD 以前の、CRT 時代の遺物だと思うのですが、LCD でも設定する必要があります。

設定する値は、画面サイズとリフレッシュレートによって変わります。

それでは、DSS を設定してみましょう。

その前に、いくつかやっておくことがあります。

a) Pad multiplexing 設定

OMAP3530 は、限られた外部ピンを、複数のモジュールで共用するようになっています。

(Pad multiplexing の超概要はこちら。)

DSS のパラレル LCD 出力は、28 本の信号線を使いますが、これらの信号が外部ピンに出るように、構成する必要があります。

u-boot のコードの中に、この設定をしている個所があったので、そのままいただいてきました。

957: MUX_VAL(CP(DSS_PCLK), (IDIS | PTD | DIS | M0))/*DSS_PCLK*/\

958: MUX_VAL(CP(DSS_HSYNC), (IDIS | PTD | DIS | M0)) /*DSS_HSYNC*/\

959: MUX_VAL(CP(DSS_VSYNC), (IDIS | PTD | DIS | M0)) /*DSS_VSYNC*/\

960: MUX_VAL(CP(DSS_ACBIAS), (IDIS | PTD | DIS | M0)) /*DSS_ACBIAS*/\

961: MUX_VAL(CP(DSS_DATA0), (IDIS | PTD | DIS | M0)) /*DSS_DATA0*/\

962: MUX_VAL(CP(DSS_DATA1), (IDIS | PTD | DIS | M0)) /*DSS_DATA1*/\

963: MUX_VAL(CP(DSS_DATA2), (IDIS | PTD | DIS | M0)) /*DSS_DATA2*/\

964: MUX_VAL(CP(DSS_DATA3), (IDIS | PTD | DIS | M0)) /*DSS_DATA3*/\

965: MUX_VAL(CP(DSS_DATA4), (IDIS | PTD | DIS | M0)) /*DSS_DATA4*/\

966: MUX_VAL(CP(DSS_DATA5), (IDIS | PTD | DIS | M0)) /*DSS_DATA5*/\

967: MUX_VAL(CP(DSS_DATA6), (IDIS | PTD | DIS | M0)) /*DSS_DATA6*/\

968: MUX_VAL(CP(DSS_DATA7), (IDIS | PTD | DIS | M0)) /*DSS_DATA7*/\

969: MUX_VAL(CP(DSS_DATA8), (IDIS | PTD | DIS | M0)) /*DSS_DATA8*/\

970: MUX_VAL(CP(DSS_DATA9), (IDIS | PTD | DIS | M0)) /*DSS_DATA9*/\

971: MUX_VAL(CP(DSS_DATA10), (IDIS | PTD | DIS | M0)) /*DSS_DATA10*/\

972: MUX_VAL(CP(DSS_DATA11), (IDIS | PTD | DIS | M0)) /*DSS_DATA11*/\

973: MUX_VAL(CP(DSS_DATA12), (IDIS | PTD | DIS | M0)) /*DSS_DATA12*/\

974: MUX_VAL(CP(DSS_DATA13), (IDIS | PTD | DIS | M0)) /*DSS_DATA13*/\

975: MUX_VAL(CP(DSS_DATA14), (IDIS | PTD | DIS | M0)) /*DSS_DATA14*/\

976: MUX_VAL(CP(DSS_DATA15), (IDIS | PTD | DIS | M0)) /*DSS_DATA15*/\

977: MUX_VAL(CP(DSS_DATA16), (IDIS | PTD | DIS | M0)) /*DSS_DATA16*/\

978: MUX_VAL(CP(DSS_DATA17), (IDIS | PTD | DIS | M0)) /*DSS_DATA17*/\

979: MUX_VAL(CP(DSS_DATA18), (IDIS | PTD | DIS | M0)) /*DSS_DATA18*/\

980: MUX_VAL(CP(DSS_DATA19), (IDIS | PTD | DIS | M0)) /*DSS_DATA19*/\

981: MUX_VAL(CP(DSS_DATA20), (IDIS | PTD | DIS | M0)) /*DSS_DATA20*/\

982: MUX_VAL(CP(DSS_DATA21), (IDIS | PTD | DIS | M0)) /*DSS_DATA21*/\

983: MUX_VAL(CP(DSS_DATA22), (IDIS | PTD | DIS | M0)) /*DSS_DATA22*/\

984: MUX_VAL(CP(DSS_DATA23), (IDIS | PTD | DIS | M0)) /*DSS_DATA23*/\

:

1013: MUX_VAL(CP(HDQ_SIO), (IDIS | PTU | EN | M4)) /*GPIO_170*/\

b) DVI 出力用電源設定 / TFP410 有効化

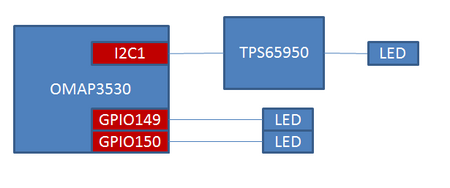

電源モジュール TPS65950 を操作して、DVI 出力のための電源供給をする必要があり、また、GPIO170 を操作して TFP410 を activate する必要があります。

これらが必要なことは、SRM に書いてありました。

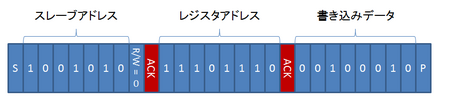

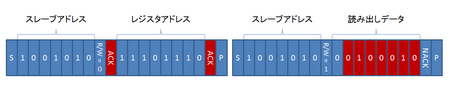

TPS65950 は、I2C1 に繋がっているので、I2C1 にコマンドを流すことによってTPS65950 を制御します。

20: /* TPS65950 settings */

21: data = 0xE0;

22: i2c_write(0x4B, 0x8E, 1, &data, 1);

23: data = 0x05;

24: i2c_write(0x4B, 0x91, 1, &data, 1);

25:

26: data = 0x20;

27: i2c_write(0x4B, 0x96, 1, &data, 1);

28: data = 0x03;

29: i2c_write(0x4B, 0x99, 1, &data, 1);

30:

31: /* activate TFP410 */

32: omap_set_gpio_direction(170, 0);

33: omap_set_gpio_dataout(170, 1);

それでは、とうとう DSS の設定です。

まずは背景画面だけを表示させてみましょう。

設定するレジスタは、以下です。

DSS_CONTROL

DISPC_IRQENABLE

DISPC_CONTROL

DISPC_DEFAULT_COLOR_0

DISPC_TIMING_H

DISPC_TIMING_V

DISPC_DIVISOR

DISPC_SIZE_LCD

110: /* clear GOLCD */

111: sr32(DISPC_CONTROL, 0, 1, 0);

DSS のレジスタのうち、シャドーレジスタと呼ばれるものは、設定した瞬間に設定値が反映されるのではなく、DISPC_CONTROL の GOLCD ビットが立った時に反映されます。

上記のレジスタでは、DISPC_DEFAULT_COLOR_0, DISPC_TIMING_H, DISPC_TIMING_V, DISPC_DIVISOR, DISPC_SIZE_LCD がシャドーレジスタになります。

シャドーレジスタを設定するときには GOLCD ビットをクリアするようにと OMAP35x TRM に書かれているので、ここで落としておきます。

113: /* use DSS1_ALWON_FCLK */

114: __raw_writel(0x0, DSS_CONTROL);

DSS_CONTROL の DISPC_CLK_SWITCH ビットにより、DSS の入力クロックを DSS1_ALWON_FCLK か DSI1_PLL_FCLK か、どちらにするかを選択できますが、DSS1_ALWON_FCLK を選択します。

DSS1_ALWON_FCLK は、DPLL4 からの出力クロックであり、自由に値を設定できます。

この値は、xloader のデフォルトでは 96MHz になっています。

96MHz だとピクセルクロックを自由に作りにくいので、今回は 432MHz にしました(別の箇所で)。

即ち、DSS の入力クロックは 432MHz ということになります。

119: /* disable interrupt */

120: __raw_writel(0x0, DISPC_IRQENABLE);

今回、割り込みは使いません。

なので、すべての割り込みを無効化しておきます。

122: /* set GPOUT1, GPOUT0, TFTDATALINES=24bit, STNTFT , LCDENABLE */

123: __raw_writel(0x18309, DISPC_CONTROL);

DISPC_CONTROL の GPOUT1, GPOUT0 ビットは、パラレル LCD 出力を、RFBI モードで使うか、バイパスモード (RFBI を使わない) で使うかを決定します。

GPOUT1, GPOUT0 の両方が立つと、バイパスモードになります。

今回はバイパスモードで使用するので、両方立てておきます。

また、LCDENABLE ビットも立てておきます。

これを立てないと、パラレル LCD 出力から出力されません。

125: /* set default color GREEN */

126: __raw_writel(0x0000ff00, DISPC_DEFAULT_COLOR(0));

背景色を、緑色にしておきます。

134: /* set H-timing */

135: __raw_writel((hbp << 20) | (hfp << 8) | hsw, DISPC_TIMING_H);

136:

137: /* set V-timing */

138: __raw_writel((vbp << 20) | (vfp << 8) | vsw, DISPC_TIMING_V);

139:

140: /* set LCD, PCD */

141: __raw_writel(0x00010000 | pcd, DISPC_DIVISOR);

142:

143: /* set LPP, PPL */

144: __raw_writel((lpp << 16) | ppl, DISPC_SIZE_LCD);

タイミング設定、ピクセルクロック設定、画面サイズ設定を行います。

これらの値は、どのようなディスプレイモードを選択するかに依存します。

また、サポートされるディスプレイモードは、LCD に依ります。

146: /* set GOLCD */

147: sr32(DISPC_CONTROL, 5, 1, 1);

シャドーレジスタに設定した値を反映させるために、GOLCD ビットを立てます。

正しく設定てきていれば、この操作により、LCD に緑色の背景画面が表示されます。

134 行目から 144 行目までのタイミング設定、ピクセルクロック設定、画面サイズ設定、これらはどのような値を設定すればよいでしょう?

まずは、LCD がどのようなディスプレイモードをサポートしているか、知る必要があります。

LCD によっては、固有の詳細情報を知らせるために、Extended Display Identification Data (EDID) というデータを提供しているものがあります。

EDID は、I2C 経由で読み出すことが出来ます。

それでは自分の LCD はどんなディスプレイモードをサポートしているのかな、と思って EDID を読んでみると、、、

I2C が read error になってしまいました。

どうやら EDID 非対応らしいです。

うーん・・・。

仕方ないので、VESA 標準タイミングのうち、適当そうなのを選んで試してみましょう。

普通の LCD は VESA 標準に従ってるはずだよね、ということで。

VESA 標準タイミングデータシートは、google で "vesa timing" で検索すると、見つけることができます。

VESA タイミングデータシート、非常に分かりやすくて、DSS で設定すべきパラメータがそのまま載っています。

ピクセルクロック値、水平/垂直フロントポーチ、同期パルス幅、バックポーチ、すべて載っています。

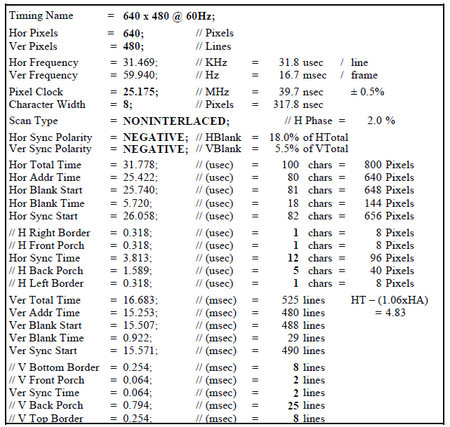

今回試してみたのは、

640 x 480 @ 60Hz

640 x 480 @ 75Hz

800 x 600 @ 60Hz

1024 x 768 @ 60Hz

1280 x 1024 @ 60Hz

です。

ピクセルクロック値は、VESA 標準で指定されている値を正確に作ることができません。

たとえば、640 x 480 @ 75Hz のピクセルクロックは 31.5MHz なのですが、DSS の入力クロック 432MHz から、この値を作ることはできません。

(ピクセルクロックは、432MHz を任意の整数で割った値を指定します。)

DSS の入力クロックを変更してやれば、正確に 31.5MHz を作れると思いますが、ちょっと手抜き。

より近い値として、432MHz を 14 で割った 30.86MHz で代用します。

この場合、画面リフレッシュレートは、73.47Hz になります。

このくらいの差だったら、まあ大丈夫でしょう、きっと。

正しく映ると、こんな感じです↓

各モードの表示結果は、こんな↓です。

| ディスプレイモード | リフレッシュレートの実際の値 | 表示結果 |

| 640 x 480 @ 60Hz | 60.14Hz | OK |

| 640 x 480 @ 75Hz | 73.47Hz | OK |

| 800 x 600 @ 60Hz | 59.22Hz | OK |

| 1024 x 768 @ 60Hz | 66.47Hz | OK |

| 1280 x 1024 @ 60Hz | 60.02Hz | OK |

1024 x 768 @ 60Hz モードでは、実際のリフレッシュレートは 60Hz からかなり外れていますが、いけるもんですね。

モノによりけりかもしれませんが。

自分のは大丈夫でした。

上の表には出ていませんが、1280 x 1024 @ 60Hz モードでは、ピクセルクロックは 108MHz にしています。

OMAP35x TRM を見ると、"Programmable pixel rate up to 75MHz" という記述があって、108MHz は上限オーバーじゃないのかと思いますが、一応、ちゃんと動いていますね。

あまりよろしくないのかもしれませんが。

ちょっと先取りしてしまいますが、640 x 480, 800 x 600, 1024 x 768, 1280 x 1024 の画面に 640 x 480 サイズの Video1 画像を表示させると、こんな風になります。

自分の LCD は、確かドット数が 1280 x 1024 だと思うので、1280 x 1024 設定以外では、DSS から送っているピクセル数と、実際のドット数が一致していません。

LCD 側で、適当に拡大して表示してくれているんですね。

・・・

背景画面が表示できたので、次はその上に Video1/Video2, Graphics 画面を表示させてみましょう。

Video1/Video2 の設定方法と、Graphics の設定方法は、ほぼ同じです。

ここでは、Video1/Video2 画面を表示するための設定方法を見てみましょう。

設定するレジスタは、以下です。

DISPC_VIDn_BA0

DISPC_VIDn_POSITION

DISPC_VIDn_SIZE

DISPC_VIDn_PICTURE_SIZE

DISPC_VIDn_FIFO_THRESHOLD

DISPC_VIDn_FIFO_SIZE_STATUS

DISPC_VIDn_ROW_INC

DISPC_VIDn_PIXEL_INC

DISPC_VIDn_ATTRIBUTES

※n は、Video1 の場合は 1, Video2 の場合は 2

159: /* clear GOLCD */

160: sr32(DISPC_CONTROL, 5, 1, 0);

設定するレジスタは、すべてシャドーレジスタなので、背景画面設定時と同じく、GOLCD ビットは落としておきます。

162: /* base address */

163: __raw_writel(ba, DISPC_VID_BA(n, 0));

Video1/Video2 の画像データを格納するアドレスを、DISPC_VIDn_BA0 に指定します。

指定するアドレスは、SRAM でも SDRAM でも大丈夫です。

DSS 内にある DMA engine は、指定されたアドレスから、画像データを DSS に継続的に転送します。

165: /* position */

166: __raw_writel((posy << 16) | posx, DISPC_VID_POSITION(n));

Video1/Video2 画面の開始座標を指定します。

一番左上が (0, 0) です。

背景画面の大きさが 1024 x 768 だとすると、一番右下は (1023, 767) です。

168: /* size */

169: __raw_writel(((sizey-1) << 16) | (sizex-1), DISPC_VID_SIZE(n));

170:

171: /* picture size */

172: __raw_writel(((orgsizey-1) << 16) | (orgsizex-1), DISPC_VID_PICTURE_SIZE(n));

表示サイズ、元画像のサイズを指定します。

Video1/Video2 は、元画像を拡大・縮小して表示する機能を持っています。

今回は、等倍で表示させるので、同じ値を設定しておきます。

(sizey == orgsizey, sizex == orgsizex)

174: /* FIFO threshold */

175: __raw_writel(0x03ff03c0, DISPC_VID_FIFO_THRESHOLD(n));

DMA engine の送り先である FIFO に関する設定です。

FIFO は、Video1, Video2 それぞれに対して存在します。

上限閾値と下限閾値を指定できて、FIFO の中身が下限閾値以下になったら DMA が開始され、上限閾値以下になったら停止します。

上の例は、上限閾値 0x3ff = 1023, 下限閾値 0x3c0 = 960 を指定しています。

OMAP35x TRM には、パフォーマンス最適化のために、上限閾値は FIFO サイズ - 1 を、下限閾値は、バースト長が 16x32bit の場合は、960 にするようにと書いてあります。

(FIFO サイズは、1024 です。)

バースト長は、この後で 16x32bit を設定します。

177: /* row inc */

178: __raw_writel(0x01, DISPC_VID_ROW_INC(n));

179:

180: /* pixel inc */

181: __raw_writel(0x01, DISPC_VID_PIXEL_INC(n));

画像領域から DMA 転送する際、今回の転送から次のデータ転送に移る時に、アドレスをどれくらい進めるかを指定します。

画像データが連続的に格納されている場合は、上記のように 1 を指定すれば OK です。

183: /* attributes */

184: __raw_writel((format << 1) | 0x8001, DISPC_VID_ATTRIBUTES(n));

DMA バースト長を 16x32bit に設定し、VIDENABLE ビットを立てます。

VIDENABLE ビットを立てることにより、Video1/Video2 画面が有効になります。

同時に、画像データのデータフォーマットを指定します。

RGB12 とか RGB24 とか ARGB とか、いろいろ選べます。

画像領域には、ここに指定したフォーマットで画像データを格納しておく必要があります。

186: /* set GOLCD */

187: sr32(DISPC_CONTROL, 5, 1, 1);

最後に、シャドーレジスタに設定した値を反映させるために、GOLCD ビットを立てます。

正しく設定てきていれば、この操作により、Video1/Video2 画面が表示されます。

Graphics 画面の設定は、Video1/Video2 画面の設定とほぼ同じなので、省略です。

後は、画像領域に正しく画像データを格納する必要がありますね。

やっぱり、好きな画像を表示させたいですよね。

以下は、任意の画像を表示させる方法です。

1. 適当な画像を用意する (フォーマットは、とりあえず何でも OK)

2. GIMP を使って、画像を表示させたい大きさに変更する

3. RAW 画像形式でファイルを保存する

4. RAW 画像形式は RGB 形式であるが、これを BGR 形式に変換する

5. 変換した画像データを SD カードにコピーしておく

6. xloader をブートさせ、画像データを SD カードから SDRAM 上の適当なアドレスに読み出す

7. 画像データを格納したアドレスを Base Address に、画像フォーマットを RGB24 (packed in 24-bit container) にするように Video1 (もしくは Video2, Graphics) 画面を設定する

こんな感じでいけますが、少々注釈です。

2 に関して

GIMP を使っていますが、画像データを RAW 画像形式で保存したいためです。

GIMP 以外でも、RAW 画像形式で保存できるものであれば OK です。

RAW 画像形式で保存したいのは、普通の画像フォーマットだと、ヘッダーとかが付加されてしまうからです。

欲しいのは、画像データのみのバイト列ですので。

3 に関して

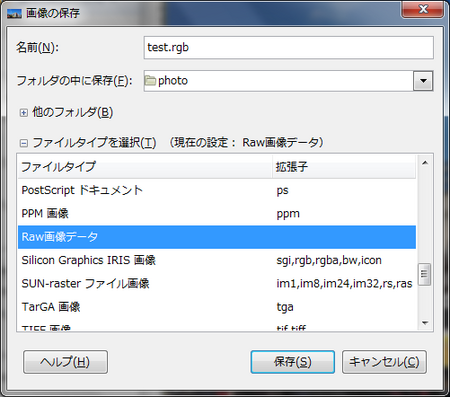

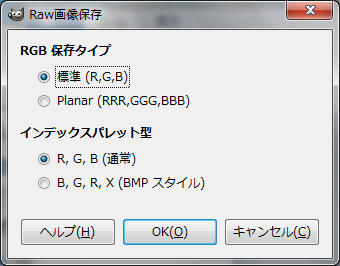

GIMP で、RAW 画像形式で保存するには、↓のように、"Raw画像データ" で保存します。

その後、↓のようなウィンドウが出てきますが、そのまま "OK" 押下です。

4 に関して

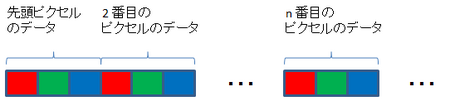

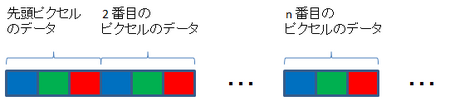

GIMP の RAW 画像形式は、RGB の順にデータが格納されます。

DSS がサポートしている RGB24 形式は、RGB 順ではなく、BGR 順です。

なので、GIMP の RAW 画像形式は、そのままでは使えません。

各ピクセルにおいて、R と B を交換する必要があります。

簡単なプログラムを書いて、RAW 画像データの R と B を入れ替えてやれば、それで OK です。

BGR 形式で保存出来るツールがあれば、ほんとはそれが一番よいのですが。

以上、注釈終わりです。

この方法を使って、Video1, Video2, Graphics 画面すべてを表示させてみました。

1280 x 1024 の背景画面に、それぞれ 640 x 512 の画像を表示させています。

せっかくなので、ちょっと重ねてみましょう。

表示優先度は、Video2 > Video1 > Graphics > 背景画面 でしたね。

ちゃんとその通りになっています↓

・・・

DSS を使って、外部 LCD に表示させてみました。

やっぱりヴィジュアルものは、動かしていて楽しいですね。

今までの UART だとかタイマーだとか、意図通り動いても、あ、動いた、くらいの感覚でしたが、LCD 表示が正しく動いた場合は、おおお、映ったあ!!となります (^-^)

beagleboard を触ろう - FAT ファイルシステム [組み込みソフト]

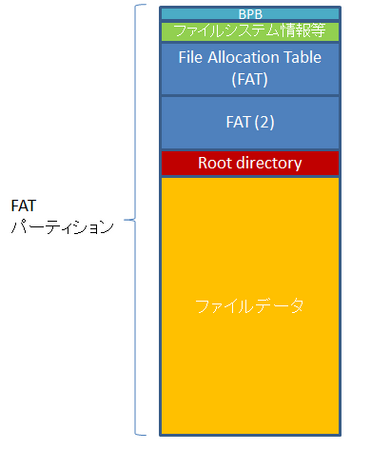

beagleboard を SD ブートさせる場合、Boot ROM コードは x-loader (MLO) を読み出し、x-loader は u-boot (u-boot.bin) を読み出し、u-boot は Linux カーネル (uImage) を読み出し、という具合に進んでいきます。

Boot ROM コード、x-loader, u-boot それぞれは、FAT ファイルシステムからファイルを読み出す能力を持っています。

x-loader の場合、FAT12/FAT16/FAT32 からファイルを読み出すことができます。

しかし、書き込みコードは実装されていません。

angstrom ブートの回で作った(そしてその後も使い続けている)ブート SD は、FAT32 でフォーマットされています。

ここでは、FAT32 の読み出しについて見ていきます。

その前に、まず、ファイルシステムを格納する SD カードについて少々。

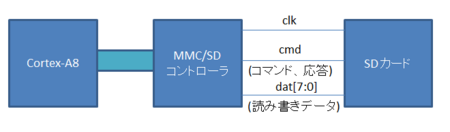

beagleboard では、SD カードに対しては、MMC/SD/SDIO ホストコントローラ (以下 MMC/SD コントローラ) 経由でアクセスします。

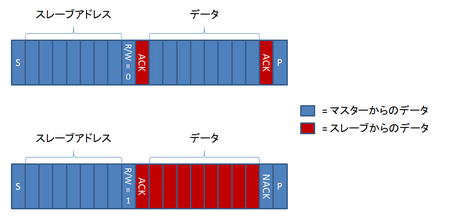

MMC/SD コントローラと SD カードは、clk, cmd, data 信号を用いてやり取りを行います。

MMC/SD コントローラが cmd 信号上にコマンドを流し、SD カードはコマンドを受け、レスポンスを同じく cmd 信号上に返し、その後 data 信号上でデータを受け渡します。

コマンドには、ブロックリード、ブロックライト、消去等のコマンドが用意されています。

基本的に、SD カードに対しては、ブロック単位の操作しかできません。

ブロックの大きさは、CMD16 (SET BLOCKLEN) コマンドを発行することにより、変更可能です(通常は 512 バイト)。

書き込みを行う際は、NAND フラッシュのように、消去してからプログラムしなければいけないという制約はありません(多分)。

内部的には、消去→プログラムを行っているのかもしれませんが、MMC/SD コントローラからは、消去しないでいきなり書き込めるようなインターフェースになっています。

SD カードを使うためには、いろいろ初期設定をしなければいけないのですが、、、

手順をあまり理解しておらず、、、

OMAP35x TRM に書いてある初期化手順と、xloader の初期化コードは手順があまり一致しないし、、、

ということで、省略です!

初期設定が完了した後は、コマンドを発行するだけで簡単にアクセスすることができます。

x-loader では、ファイルを読み出す際に、CMD17 (READ SINGLE BLOCK) を発行して、1 ブロック(512 バイト)を読み出しています。

・・・

SD カードの先頭セクタ(先頭ブロック)は、MBR (Master Boot Record) と呼ばれる領域です。